I do not know what exactly system-clock-frequency does and whether it is safe in this context. The yaml description talks about fixed mclk.

This is my dts for i2s:

i2s_8ch_0: i2s@ff300000 {

compatible = "rockchip,rk3308-i2s-tdm";

reg = <0x0 0xff300000 0x0 0x1000>;

interrupts = <GIC_SPI 48 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&cru SCLK_I2S0_8CH_TX>, <&cru SCLK_I2S0_8CH_RX>, <&cru HCLK_I2S0_8CH>,

<&cru SCLK_I2S0_8CH_TX_SRC>,

<&cru SCLK_I2S0_8CH_RX_SRC>,

<&cru PLL_VPLL0>,

<&cru PLL_VPLL1>;

clock-names = "mclk_tx", "mclk_rx", "hclk",

"mclk_tx_src", "mclk_rx_src",

"mclk_root0", "mclk_root1";

dmas = <&dmac1 0>, <&dmac1 1>;

dma-names = "tx", "rx";

resets = <&cru SRST_I2S0_8CH_TX_M>, <&cru SRST_I2S0_8CH_RX_M>;

reset-names = "tx-m", "rx-m";

rockchip,cru = <&cru>;

rockchip,grf = <&grf>;

//rockchip,mclk-calibrate;

rockchip,trcm-sync-tx-only;

pinctrl-names = "default";

pinctrl-0 = <&i2s_8ch_0_sclktx

&i2s_8ch_0_sclkrx

&i2s_8ch_0_lrcktx

&i2s_8ch_0_lrckrx

&i2s_8ch_0_sdi0

&i2s_8ch_0_sdi1

&i2s_8ch_0_sdi2

&i2s_8ch_0_sdi3

&i2s_8ch_0_sdo0

&i2s_8ch_0_sdo1

&i2s_8ch_0_sdo2

&i2s_8ch_0_sdo3

&i2s_8ch_0_mclk>;

status = "ok";

};

Does the alsa device still exist, is it created?

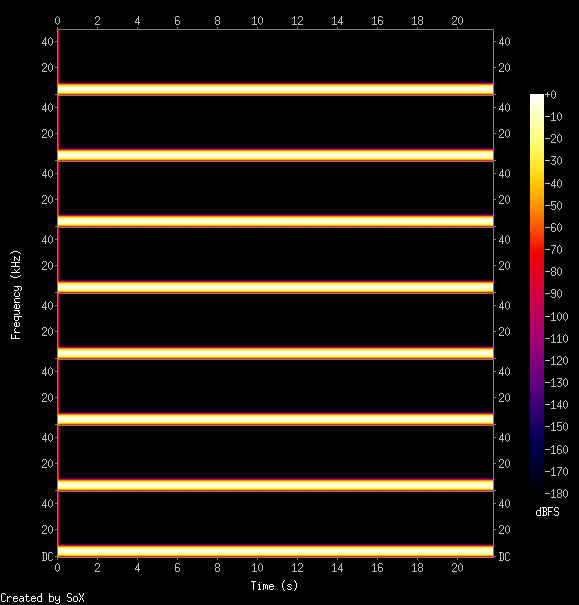

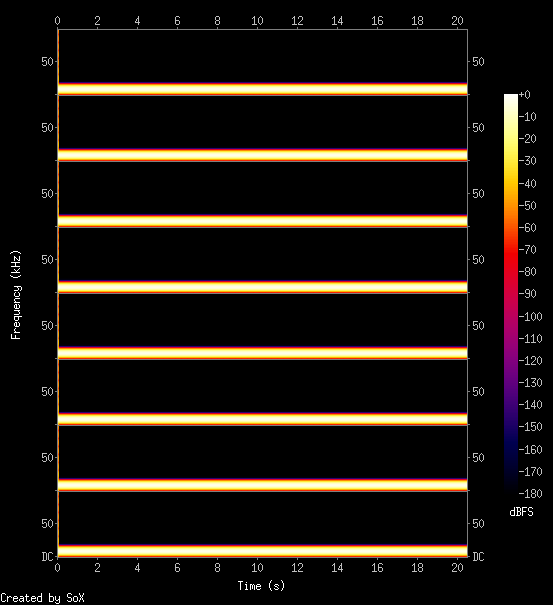

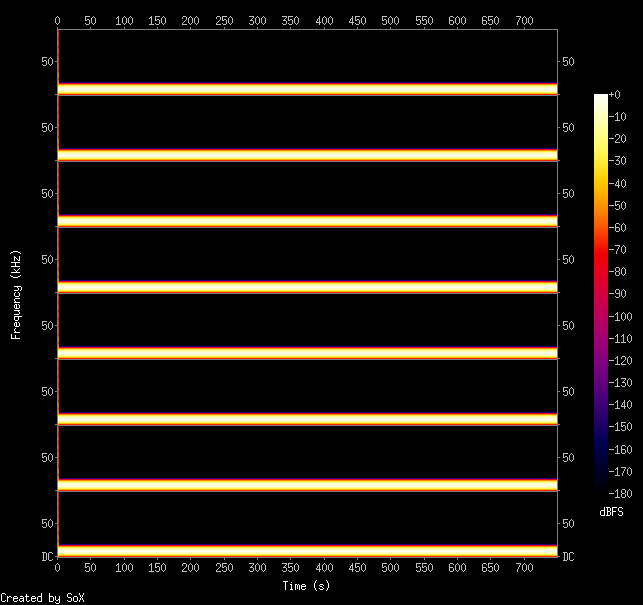

Does the playback device run OK?