Turns out that CPU clocks can actually be increased by modifying the OPP tables in firmware - they are not hardcoded as I initially thought. Here’s a rough guide:

-

Clone the

edk2,edk2-platformsandedk2-non-osirepositories from https://github.com/radxa and follow the build instructions inedk2-non-osi/Platform/CIX/Sky1/Readme.md -

Copy

edk2-non-osi/Platform/CIX/Sky1/PackageTool/pm_config/toedk2-platforms/Platform/Radxa/Orion/O6/pm_config/ -

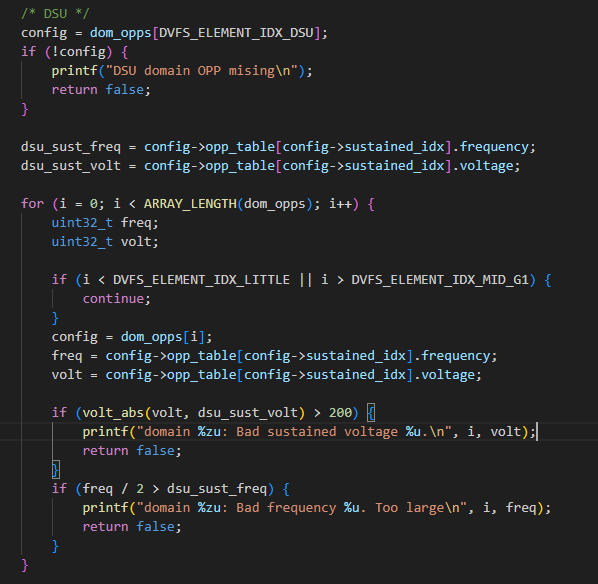

Open

opp_config_custom.hinside the copiedpm_configdirectory -

Set

#define PM_OPP_TABLE_CONFIG 1 -

Tweak the frequency and voltage levels in the defined OPP tables (at your own risk!)

-

dxs_lit- little cluster -

dxs_gb0- big cluster 0 -

dxs_gb1- big cluster 1 -

dxs_gm0- medium cluster 0 -

dxs_gm1- medium cluster 1

-

-

Rebuild and flash the generated firmware

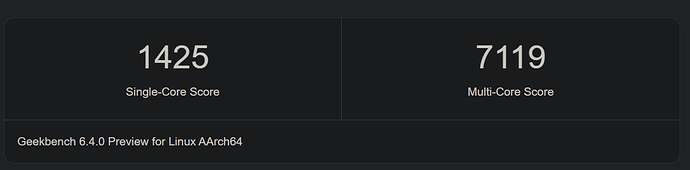

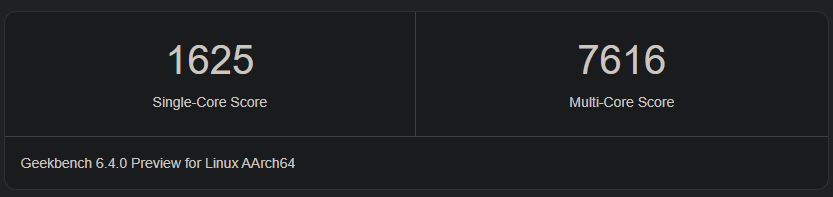

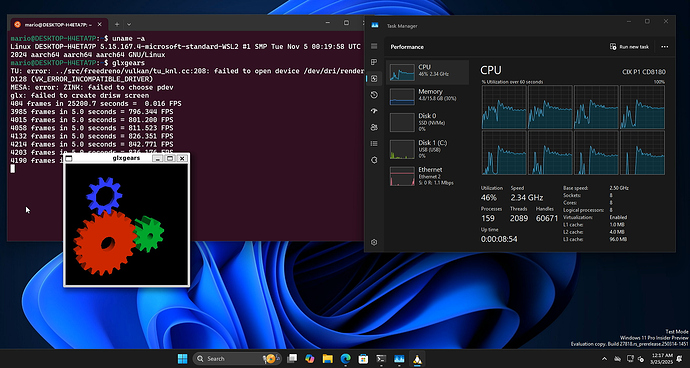

Here’s a GB6 run with the big clusters set to 2.8, medium to 2.4 and little to 1.8 GHz:

Radxa Computer (Shenzhen) Co., Ltd. Radxa Orion O6 - Geekbench