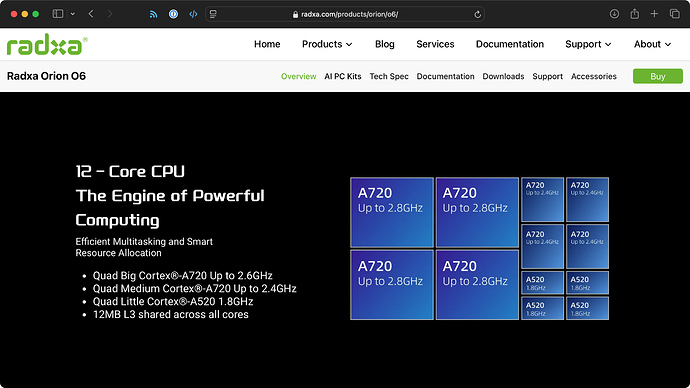

Well, I’m sorry, but 2.5+2.6 and 2.2+2.3 are clearly not the advertised 2.8+2.4, so for me “overclocking” is running beyond 2.8+2.4. I understand limitations caused by manufacturing defects of early batches but in this case it would be wiser to let the customers configure both the DRAM and the CPU frequencies in the BIOS (like is done in the PC world), pre-set them to safe values and tell them “above is at your own risk”. Many of us would happily run at whatever is stable for us and not just according the the maker’s specs targetting harsher operating conditions.

You guys need to keep in mind that the only reason customers are willing to invest quite some money in this board is to get real performance because that is their metric for this product. It’s not a rock5b that someone uses as their small NAS or video player. They’re ordering this machine as a development machine because it advertises performance getting close to the x86 world but with an Arm chip. If customers just want an ITX board they buy an x86. Here they’re specifically targetting Arm and performance. Thus you can be sure that for a lot of them, while stability is super important, performance will also be and many will want to run at (or even beyond) advertised specs as long as it works for them.

You’ll also note that nobody complained about the power draw under load. There are complaints in idle because the machine is supposed to stay up all time and not to make noise close to where the developers operate, but if it draws 30W at full load, that’s OK because it will not be all the time.

And the real benefit of this is for both Radxa and CIX: do you know who posts performance numbers? Precisely those interested with this and who are proud to break new records, thus a lot of the great publicity for your board and that chip will actually be made by users running above specs and comparing them with competition.