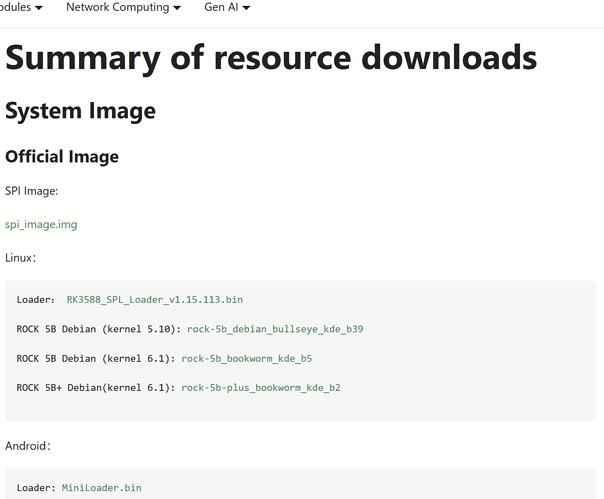

Hi, at https://docs.radxa.com/en/rock5/rock5b/download I see mentioned " Loader: RK3588_SPL_Loader_v1.15.113.bin".

Inside the directory view for this file rk3588_spl_loader_v1.15.113.bin at https://dl.radxa.com/rock5/sw/images/loader/rock-5b/release/ , I see that its date is recent - 2024-05-23. Definitely I have not installed this recent version.

In the same directory is a file “rock-5b-spi-image-gd1cf491-20240523.img”, with the same date 2024-05-23.

The clear and easy to understand installation instructions I find on the Wiki are for the SPI but not for the SPL: https://wiki.radxa.com/Rock5/install/spi#Simple_method

I see a mentioning of flashing the SPI and SPL file at the same time through the Maskrom mode via the USB port.

Can you please clarify, does the SPI flash file contain the SPL flash image too, so when I follow the “Simple method” SPI installation steps, the SPL is upgraded too?

Or, after going through the SPI installation steps which are from Linux running locally on the Rock5B, must I also shut down the Rock5B, connect it to another computer via MaskROM USB mode, and flash the SPI image separately via one of the tools prescribed? If you can detail this requirement and steps would be appreciated.

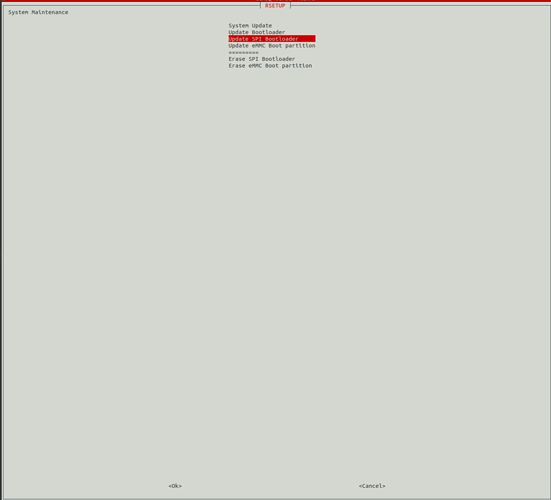

At the bottom of https://wiki.radxa.com/Rock5/install/spi I see a description that “RKDevTool” GUI is used on WIndows to flash the SPL file, then click “Erase all” and reboot.

Alternatively I see “rkdeveloptool db rk3588_spl_loader_v1.08.111.bin; rkdeveloptool wl 0 zero.img; rkdeveloptool rd” done in Linux - that must be Linux on a separate computer which is connected to the Rock5B in MaskROM mode via USB.

Do I need to go through these steps, or have I already updated the SPL implicitly as I asked above, or will just keeping an old SPL version be fine in all situations (boot via NVMe etc.)?

Many thanks

Digging a bit, I am told that the SPL is indeed separate from the SPI, and can only be flashed from another computer via USB MaskRom mode.

So the steps are as shown on this screenshot https://wiki.radxa.com/mw/images/c/c8/Eraseall_new.png :

First click the “Advanced function” tab.

Then specify the filename of the SPL loader file.

Then click “Download”.

Then click “EraseAll” and then click “ResetDevice”, and that’s all.

Did I get it right

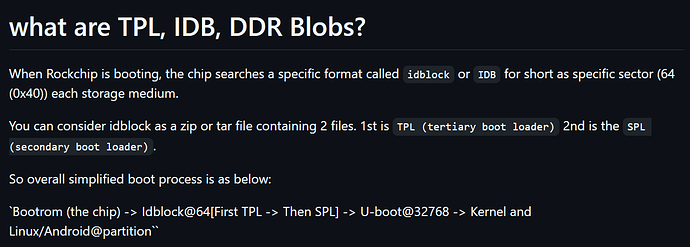

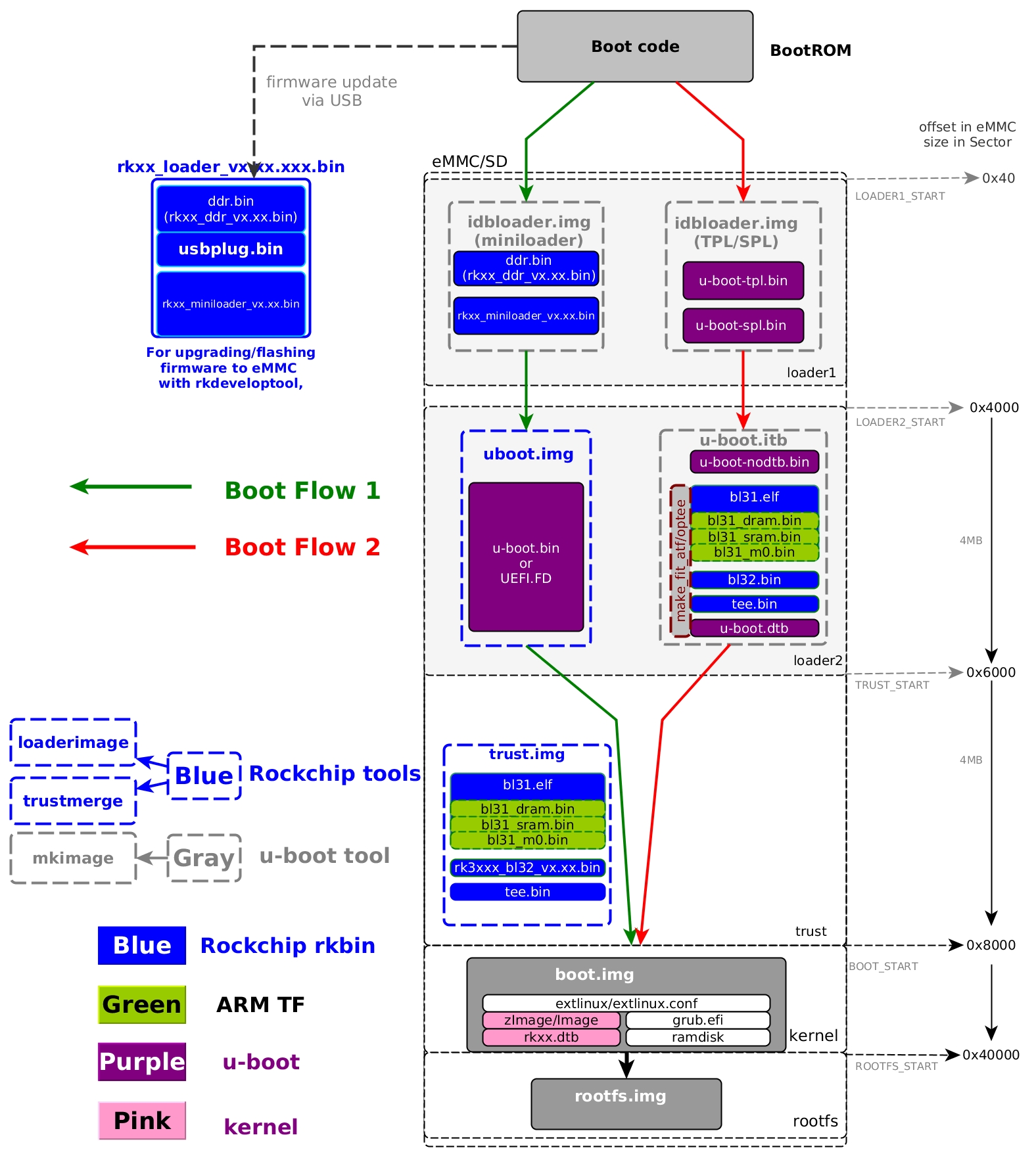

An expert says “The spl loader is just a specially packed u-boot. I’m not familiar with the precise ins and outs of the downstream tooling and binaries, as I only use mainline stuff. “SPL” can mean both a stage of u-boot (so it would be part of your SPI flash’s u-boot) or it can also refer to the u-boot that gets loaded over USB into memory temporarily just to actually do any other operations on the board while flashing.”

Oh I got it, there was even more confusion.

So the way RockChip use the term “SPL”, it is only a transient boot code used specifically to kickstart the RK3588 during boot via USB MaskRom.

SPL is never a part of an RK3588’s normal boot process. It is only a MaskRom boot process thing.

Therefore, the SPL is not updated to a Rock5B board.

Meanwhile the “spi-image.bin” file advertised, is an u-boot distribution to be flashed to the Rock5B’s SPI flash chip.

Due to the above, I find it a bit confusing that the SPL version and filename is listed at https://docs.radxa.com/en/rock5/rock5b/download rather than the SPI. The SPI should be downloaded and flashed to have a recent UBoot onboard on the Rock5B especially to get NVMe boot support, while the SPL is a pure special purpose file, not used by normal users (aside from advanced mode SPI flashing via USB in MaskRom mode).

@RadxaYuntian What about on the Download page you show the SPI instead of the SPL file?

Thanks

Reading https://docs.radxa.com/en/rock5/rock5b/download one more time, I see now that the SPI file is linked above the SPL but the formatting is broken and a bit ocnfusing.