Thanks Stephen, for pointing me to the commit hash and the tip to disable the u-boot log.

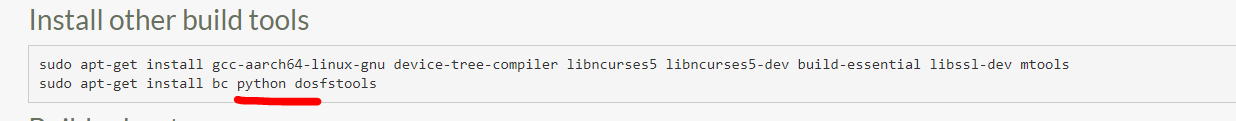

In the process of testing again, I found my underlying issue which was that my build machine was missing python2 which prevented a successful u-boot itb. I was following the directions here: https://wiki.radxa.com/Rock3/dev/Debian

which shows the required build tools includes “python” and I did not realize I needed python2.

This may be useful to someone else trying to build u-boot, until the wiki page is updated

also, I added CONFIG_DISABLE_CONSOLE=y which did stop some of the console output. Here is what I am still getting. At least I can build u-boot now and make adjustments as needed. Thanks again

DDR Version V1.10 20210810

ln

ddrconfig:0

LPDDR4X, 324MHz

BW=32 Col=10 Bk=8 CS0 Row=16 CS=1 Die BW=16 Size=2048MB

tdqss: cs0 dqs0: -24ps, dqs1: -96ps, dqs2: -96ps, dqs3: -168ps,

change to: 324MHz

PHY drv:clk:36,ca:36,DQ:29,odt:60

vrefinner:16%, vrefout:41%

dram drv:40,odt:0

clk skew:0x63

change to: 528MHz

PHY drv:clk:36,ca:36,DQ:29,odt:60

vrefinner:16%, vrefout:41%

dram drv:40,odt:0

clk skew:0x58

change to: 780MHz

PHY drv:clk:36,ca:36,DQ:29,odt:60

vrefinner:16%, vrefout:41%

dram drv:40,odt:0

clk skew:0x58

change to: 1056MHz(final freq)

PHY drv:clk:36,ca:36,DQ:29,odt:60

vrefinner:16%, vrefout:22%

dram drv:40,odt:80

vref_ca:00000071

clk skew:0x39

cs 0:

the read training result:

DQS0:0x38, DQS1:0x39, DQS2:0x3c, DQS3:0x35,

min : 0xb 0xb 0xd 0xc 0x1 0x3 0x6 0x3 , 0x6 0x6 0x2 0x2 0xa 0x9 0x c 0x7 ,

0xf 0xd 0xc 0xa 0x5 0x2 0x4 0x5 , 0xa 0x7 0x6 0x2 0xd 0xd 0x a 0xd ,

mid :0x28 0x28 0x29 0x28 0x1d 0x20 0x23 0x20 ,0x23 0x23 0x1f 0x1e 0x27 0x27 0x2 9 0x25 ,

0x2c 0x2b 0x29 0x27 0x22 0x1f 0x21 0x23 ,0x26 0x23 0x22 0x1e 0x29 0x29 0x2 7 0x29 ,

max :0x45 0x46 0x46 0x44 0x3a 0x3d 0x40 0x3d ,0x41 0x41 0x3d 0x3a 0x44 0x45 0x4 6 0x43 ,

0x49 0x49 0x46 0x45 0x40 0x3d 0x3e 0x41 ,0x42 0x3f 0x3f 0x3a 0x46 0x46 0x4 5 0x45 ,

range:0x3a 0x3b 0x39 0x38 0x39 0x3a 0x3a 0x3a ,0x3b 0x3b 0x3b 0x38 0x3a 0x3c 0x3 a 0x3c ,

0x3a 0x3c 0x3a 0x3b 0x3b 0x3b 0x3a 0x3c ,0x38 0x38 0x39 0x38 0x39 0x39 0x3 b 0x38 ,

the write training result:

DQS0:0x36, DQS1:0x2d, DQS2:0x2d, DQS3:0x23,

min :0x5c 0x5f 0x60 0x5d 0x53 0x57 0x59 0x5b 0x59 ,0x4f 0x50 0x4b 0x4a 0x53 0x5 3 0x54 0x54 0x4e ,

0x53 0x54 0x50 0x50 0x4a 0x48 0x4a 0x50 0x4e ,0x4b 0x48 0x47 0x44 0x4d 0x4 e 0x4c 0x4f 0x48 ,

mid :0x79 0x7b 0x7d 0x79 0x70 0x73 0x75 0x76 0x74 ,0x6d 0x6d 0x67 0x67 0x70 0x7 0 0x70 0x70 0x6b ,

0x71 0x71 0x6c 0x6d 0x66 0x63 0x66 0x6b 0x6a ,0x68 0x64 0x62 0x5f 0x6a 0x6 a 0x67 0x6b 0x64 ,

max :0x97 0x98 0x9a 0x96 0x8e 0x90 0x92 0x91 0x90 ,0x8b 0x8a 0x84 0x84 0x8d 0x8 d 0x8d 0x8d 0x88 ,

0x8f 0x8f 0x89 0x8a 0x83 0x7f 0x82 0x86 0x87 ,0x85 0x81 0x7e 0x7b 0x87 0x8 7 0x83 0x88 0x81 ,

range:0x3b 0x39 0x3a 0x39 0x3b 0x39 0x39 0x36 0x37 ,0x3c 0x3a 0x39 0x3a 0x3a 0x3 a 0x39 0x39 0x3a ,

0x3c 0x3b 0x39 0x3a 0x39 0x37 0x38 0x36 0x39 ,0x3a 0x39 0x37 0x37 0x3a 0x3 9 0x37 0x39 0x39 ,

CA Training result:

cs:0 min :0x52 0x52 0x48 0x48 0x49 0x47 0x47 ,0x4f 0x4d 0x45 0x43 0x46 0x42 0x4 7 ,

cs:0 mid :0x90 0x91 0x86 0x87 0x86 0x85 0x76 ,0x8d 0x8c 0x83 0x82 0x83 0x80 0x7 5 ,

cs:0 max :0xcf 0xd1 0xc4 0xc6 0xc4 0xc3 0xa5 ,0xcb 0xcb 0xc1 0xc1 0xc1 0xbf 0xa 3 ,

cs:0 range:0x7d 0x7f 0x7c 0x7e 0x7b 0x7c 0x5e ,0x7c 0x7e 0x7c 0x7e 0x7b 0x7d 0x5 c ,

out

INFO: Preloader serial: 2

NOTICE: BL31: v2.3():v2.3-181-gc9a647cae:cl

NOTICE: BL31: Built : 10:55:41, Oct 18 2021

INFO: GICv3 without legacy support detected.

INFO: ARM GICv3 driver initialized in EL3

INFO: pmu v1 is valid

INFO: dfs DDR fsp_param[0].freq_mhz= 1056MHz

INFO: dfs DDR fsp_param[1].freq_mhz= 324MHz

INFO: dfs DDR fsp_param[2].freq_mhz= 528MHz

INFO: dfs DDR fsp_param[3].freq_mhz= 780MHz

INFO: Using opteed sec cpu_context!

INFO: boot cpu mask: 0

INFO: BL31: Initializing runtime services

WARNING: No OPTEE provided by BL2 boot loader, Booting device without OPTEE init ialization. SMC`s destined for OPTEE will return SMC_UNK

ERROR: Error initializing runtime service opteed_fast

INFO: BL31: Preparing for EL3 exit to normal world

INFO: Entry point address = 0xa00000

INFO: SPSR = 0x3c9