The Radxa image that i use b24.

I fixed overlay for MCP2515 for my oscillator frequency and interrupt pin, then loaded it.

/ {

metadata {

title = "Enable MCP2515 SPI3M0 to CAN";

compatible = "rockchip,rk3566\0rockchip,rk3568";

category = "misc";

description = "Enable MCP2515 SPI3M0 to CAN With 12M Crystal Oscillator.";

};

fragment@0 {

target = <0xffffffff>;

__overlay__ {

mcp2515_int_pin {

mcp2515_int_pin {

rockchip,pins = <0x03 0x1d 0x00 0xffffffff>;

phandle = <0x02>;

};

};

};

};

fragment@1 {

target-path = [2f 00];

__overlay__ {

can-mcp2515-osc {

compatible = "fixed-clock";

clock-frequency = <0x1312d00>;

#clock-cells = <0x00>;

phandle = <0x01>;

};

};

};

fragment@2 {

target = <0xffffffff>;

__overlay__ {

status = "okay";

max-freq = <0x7735940>;

#address-cells = <0x01>;

#size-cells = <0x00>;

pinctrl-0 = <0xffffffff 0xffffffff>;

pinctrl-1 = <0xffffffff 0xffffffff>;

can-mcp2515@0 {

status = "okay";

compatible = "microchip,mcp2515";

reg = <0x00>;

interrupt-parent = <0xffffffff>;

interrupts = <0x10 0x08>;

spi-max-frequency = <0x7a1200>;

clocks = <0x01>;

vdd-supply = <0xffffffff>;

xceiver-supply = <0xffffffff>;

pinctrl-names = "default";

pinctrl-0 = <0x02>;

phandle = <0x03>;

};

};

};

__symbols__ {

mcp2515_int_pin = "/fragment@0/__overlay__/mcp2515_int_pin/mcp2515_int_pin";

can_mcp2515_osc = "/fragment@1/__overlay__/can-mcp2515-osc";

can_mcp2515 = "/fragment@2/__overlay__/can-mcp2515@0";

};

__fixups__ {

pinctrl = "/fragment@0:target:0";

pcfg_pull_none = "/fragment@0/__overlay__/mcp2515_int_pin/mcp2515_int_pin:rockchip,pins:12";

spi3 = "/fragment@2:target:0";

spi3m0_cs0 = "/fragment@2/__overlay__:pinctrl-0:0\0/fragment@2/__overlay__:pinctrl-1:0";

spi3m0_pins = "/fragment@2/__overlay__:pinctrl-0:4";

spi3m0_pins_hs = "/fragment@2/__overlay__:pinctrl-1:4";

gpio4 = "/fragment@2/__overlay__/can-mcp2515@0:interrupt-parent:0";

vcc3v3_sys = "/fragment@2/__overlay__/can-mcp2515@0:vdd-supply:0\0/fragment@2/__overlay__/can-mcp2515@0:xceiver-supply:0";

};

__local_fixups__ {

fragment@2 {

__overlay__ {

can-mcp2515@0 {

clocks = <0x00>;

pinctrl-0 = <0x00>;

};

};

};

};

};

And it works))

[ 3.870820] mcp251x spi3.0: Looking up vdd-supply from device tree

[ 3.870908] mcp251x spi3.0: Linked as a consumer to regulator.2

[ 3.870913] mcp251x spi3.0: Looking up xceiver-supply from device tree

[ 3.940694] mcp251x spi3.0: CANCTRL 0x87

[ 3.942029] mcp251x spi3.0 can0: MCP2515 successfully initialized.

[ 4.255702] mcp251x spi3.0: CNF: 0x00 0x92 0x02

Then

ip link set dev can0 up type can bitrate 1000000

In candump i see received CAN messages. But …

A lot of CAN messages comes in wrong order or just lose.

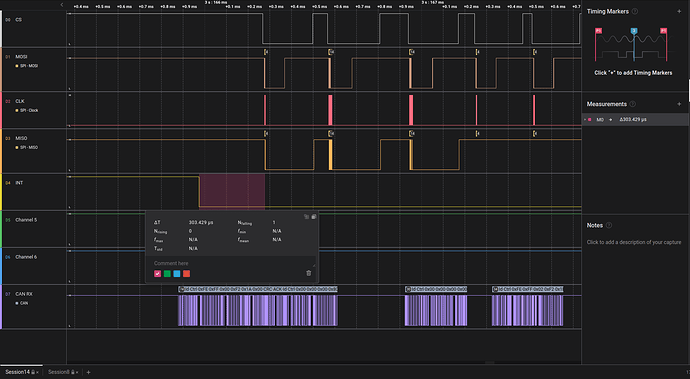

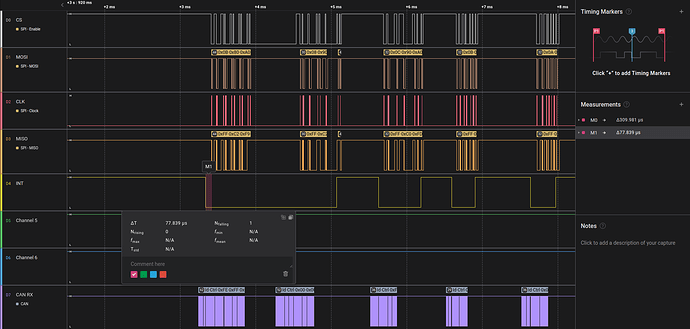

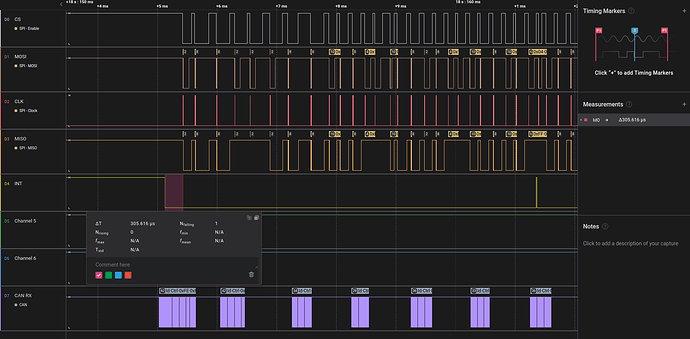

That what i see in logic analyzer on SPI bus between MCP and Radxa:

CAN frequency: 1MHz

SPI frequency: 8MHz

How it can be seen on sreenshot above, there is delay between getting INTerrupt from MCP2515 and

pulling CS pin down. The delay is about 300 µs. During this time MCP2515 gets almost 4 CAN messages. But there is only 2 receive buffers to store messages in MCP2515.

MCP says me:

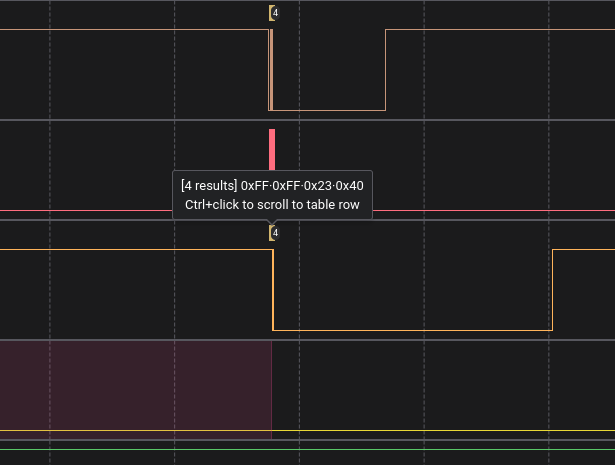

That means buffers overflow)

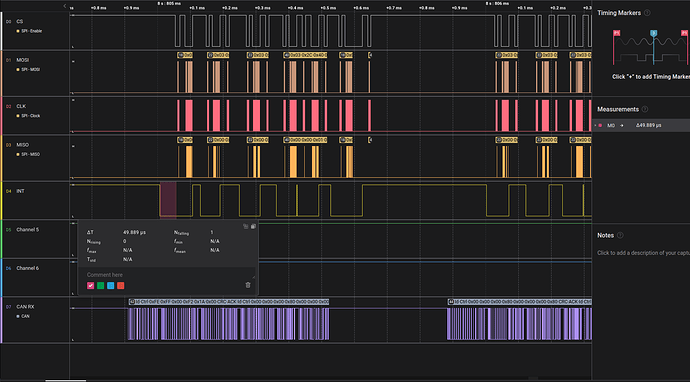

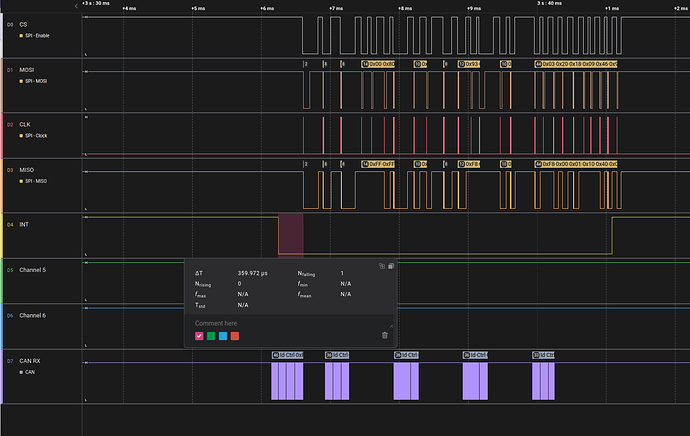

I have RPI CM3+ with the same connection scheme. It works ok:

The delay is only 50 µs and all CAN messages are received in the correct order without loss

I thought it might be the MCP driver, but on the RPi+ it’s the same driver, at least it hasn’t changed since 2018 ))

What can be wrong?

Help

buuut …

buuut …