My oldest 5V SBC power brick with A-to-C cable:

in0: 5.00 V (min = +5.00 V, max = +5.00 V)

curr1: 0.00 A (max = +0.00 A)

in_voltage0_raw: 4081

in_voltage1_raw: 4093

in_voltage2_raw: 3275

in_voltage3_raw: 4

in_voltage4_raw: 4089

in_voltage5_raw: 3237

in_voltage6_raw: 888 -> 888 / 175 = 5.07

in_voltage7_raw: 1724

RPi USB-C power brick:

in0: 5.00 V (min = +5.00 V, max = +5.00 V)

curr1: 3.00 A (max = +3.00 A)

in_voltage0_raw: 4082

in_voltage1_raw: 4092

in_voltage2_raw: 3042

in_voltage3_raw: 4

in_voltage4_raw: 4092

in_voltage5_raw: 2435

in_voltage6_raw: 927 -> 927 / 175 = 5.3

in_voltage7_raw: 1169

Apple 96W charger:

in0: 9.00 V (min = +9.00 V, max = +9.00 V)

curr1: 3.00 A (max = +3.00 A)

in_voltage0_raw: 4080

in_voltage1_raw: 4093

in_voltage2_raw: 3282

in_voltage3_raw: 4

in_voltage4_raw: 4088

in_voltage5_raw: 3238

in_voltage6_raw: 1565 -> 1565 / 175 = 8.94

in_voltage7_raw: 1988

24W charger with default DT (maxing out at 12V):

in0: 12.00 V (min = +12.00 V, max = +12.00 V)

curr1: 1.50 A (max = +1.50 A)

in_voltage0_raw: 4080

in_voltage1_raw: 4094

in_voltage2_raw: 3283

in_voltage3_raw: 3194

in_voltage4_raw: 4094

in_voltage5_raw: 3227

in_voltage6_raw: 2096 -> 2096 / 175 = 11.98

in_voltage7_raw: 2376

24W charger with adjusted sink-pdos DT entries:

in0: 15.00 V (min = +15.00 V, max = +15.00 V)

curr1: 1.60 A (max = +1.60 A)

in_voltage0_raw: 4080

in_voltage1_raw: 4090

in_voltage2_raw: 3277

in_voltage3_raw: 6

in_voltage4_raw: 4088

in_voltage5_raw: 3234

in_voltage6_raw: 2625 -> 2625 / 175 = 15

in_voltage7_raw: 2418

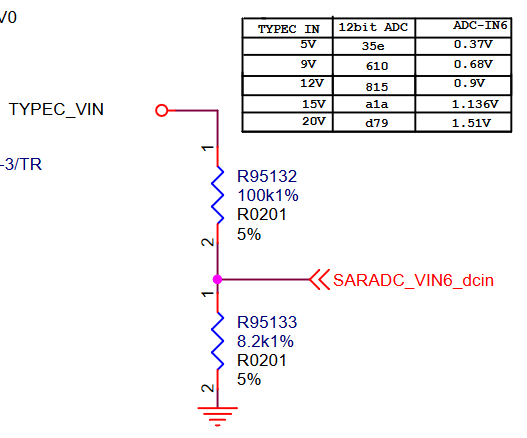

The 175 divider I just pulled out of nowhere…