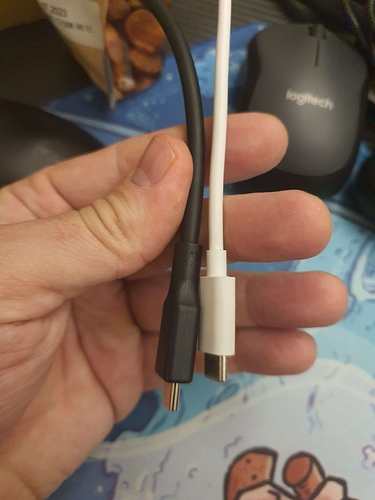

Well, I feel like I made some progress. I was able to hook up a serial to USB cable to the UART pins and boot (https://wiki.radxa.com/Rock5/dev/serial-console). Here’s what I saw:

DDR Version V1.08 20220617

LPDDR4X, 2112MHz

channel[0] BW=16 Col=10 Bk=8 CS0 Row=17 CS1 Row=17 CS=2 Die BW=8 Size=4096MB

channel[1] BW=16 Col=10 Bk=8 CS0 Row=17 CS1 Row=17 CS=2 Die BW=8 Size=4096MB

channel[2] BW=16 Col=10 Bk=8 CS0 Row=17 CS1 Row=17 CS=2 Die BW=8 Size=4096MB

channel[3] BW=16 Col=10 Bk=8 CS0 Row=17 CS1 Row=17 CS=2 Die BW=8 Size=4096MB

Manufacturer ID:0x6

CH0 RX Vref:27.7%, TX Vref:23.8%,23.8%

CH1 RX Vref:28.7%, TX Vref:23.8%,23.8%

CH2 RX Vref:29.7%, TX Vref:24.8%,24.8%

CH3 RX Vref:27.7%, TX Vref:23.8%,23.8%

change to F1: 528MHz

change to F2: 1068MHz

change to F3: 1560MHz

change to F0: 2112MHz

out

INFO: Preloader serial: 2

NOTICE: BL31: v2.3():v2.3-405-gb52c2eadd:derrick.huang

NOTICE: BL31: Built : 11:23:47, Aug 15 2022

INFO: spec: 0x1

INFO: ext 32k is not valid

INFO: GICv3 without legacy support detected.

INFO: ARM GICv3 driver initialized in EL3

INFO: system boots from cpu-hwid-0

INFO: idle_st=0x21fdf, pd_st=0x11fff9, repair_st=0xfff70001

INFO: dfs DDR fsp_params[0].freq_mhz= 2112MHz

INFO: dfs DDR fsp_params[1].freq_mhz= 528MHz

INFO: dfs DDR fsp_params[2].freq_mhz= 1068MHz

INFO: dfs DDR fsp_params[3].freq_mhz= 1560MHz

INFO: BL31: Initialising Exception Handling Framework

INFO: BL31: Initializing runtime services

WARNING: No OPTEE provided by BL2 boot loader, Booting device without OPTEE initialization. SMC`s destined for OPTEE will return SMC_UNK

ERROR: Error initializing runtime service opteed_fast

INFO: BL31: Preparing for EL3 exit to normal world

INFO: Entry point address = 0x200000

INFO: SPSR = 0x3c9

Not sure what to make of this. I think this is the debian image (latest).