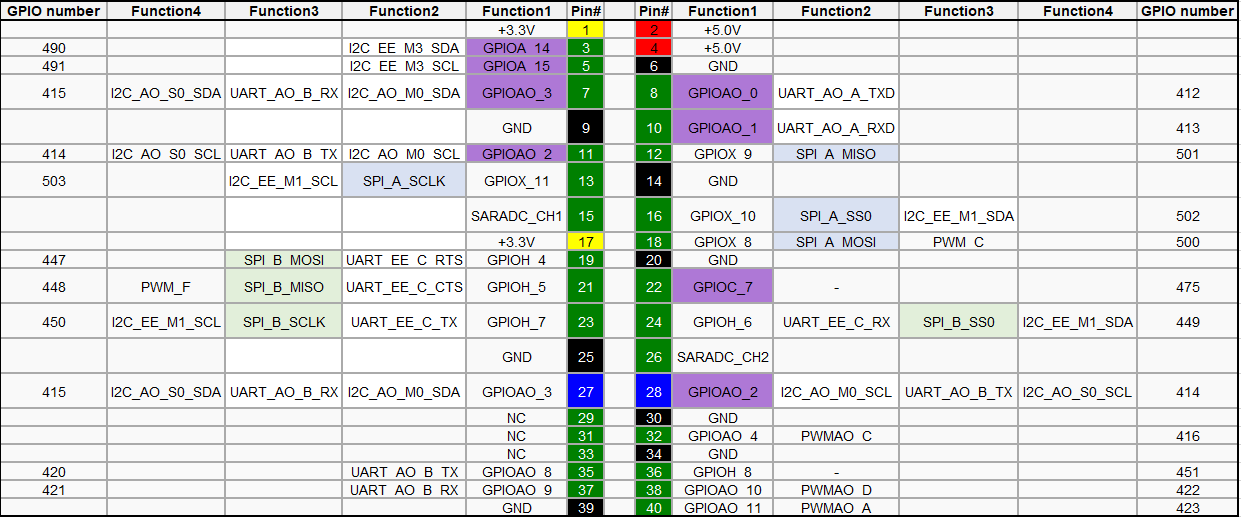

I am planning to use both SPI interfaces /spi0.0 and /spi1.0 on the Zero. So header pins 12, 13, 16, 18, 19, 21, 23, 24 will be dedicated for SPI.

I have 8 SPI peripherals that I need to retrieve data from at any time so I’ll need 8 chipselect signals. Can I use any of the remaining header pins (labeled GPIO under Function1) as a chipselect signal for the SPI peripherals?