“- 1 x 5V DC power in”

This is an error and we have fixed it. The GPIO 5V of X4 can only output power but not feed in power.

“- 1 x 5V DC power in”

This is an error and we have fixed it. The GPIO 5V of X4 can only output power but not feed in power.

Ty for the quick feedback!

Have a great day

Looking again at the spec I could see that there’s a BOOTSEL button to program the rp2040. So I believe that the rp2040 is connected to the n100 via usb and appears as storage when you press this button.

But that’s only a guess for now!

If this is the same as the X2L you are right.

Does this board support HDMI-CEC, and can I use the RPI5 power supply with it?

No ideas about CEC.

But for the RPi5 power supply, the European has 12V output listed on it, which the Radxa X4 requires. But the protocol isn’t specified, so if it’s PD it should work.

More context to my question here:

I’m guessing the X4 has the same capability to reset the RP2040 via X86 GPIO

On the X2L you push a button.

There was no mystery there, just look at the X4 schematics/datasheet

I see in the schematic (page 6) that RST_RP2040 is connected to GPP_B17. Can you teach me how I translate this to which GPIO I have to change on the x86 side of things?

I don’t have the board on hand yet and can’t list the GPIO chips / pins.

I just meant that it’s not a mystery that RP2040 is connected via USB (it’s on page 3).

Ah, got it. Yeah, I already knew that also.

X4 doesn’t support HDMI CEC because most Intel SoC doesn’t support HDMI CEC including Alder Lake.

Hi,

I’ve noticed that the 12V input header next to the usb-c port seems to be missing from the mechanical drawings in the product brief and on the step model.

Have a good day!

The memory benchmarks in your run are way faster than my own (though I’ve been seeing a lot of thermal issues with my setup)—is that a difference between X4L versus X4, in terms of the memory chip(s) being used?

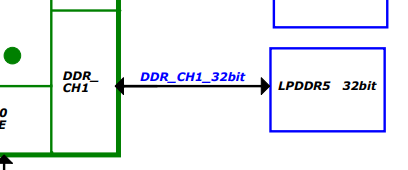

The memory width of X4 is half of that of X4L, which is 32bit vs 64bit. So the X4 only has half a channel. I think this may be related to the small size of the board, so there is no room for more traces.

##########################################################################

DIMM configuration:

*-bank:0

description: [empty]

physical id: 0

slot: Controller0-ChannelA-DIMM0

*-bank:1

description: [empty]

physical id: 1

slot: Controller0-ChannelB-DIMM0

*-bank:2

description: DIMM LPDDR4 Synchronous 6400 MHz (0.2 ns)

vendor: SK Hynix

physical id: 2

configured speed: 4800MT/s

size: 4GiB

width: 16 bits

clock: 2105MHz (0.5ns)

*-bank:3

description: DIMM LPDDR4 Synchronous 6400 MHz (0.2 ns)

vendor: SK Hynix

physical id: 3

configured speed: 4800MT/s

size: 4GiB

width: 16 bits

clock: 2105MHz (0.5ns)

Hi Jeff,

I follow you since years and I really like most of your videos.

But I think you are by far to positive about Raspberry Pi (for example the 5 is sucking a lot of electricity for not a lot of power, the cost is far from the initial promise, broadcom model used is a joke, the stock exchange entry is build from the community etc…), so let me ask what are you doing here, usually you are promoting the Raspberry products?

Don’t waste your time answering anyway, I like very much your videos, but I can breathe now I told you what I think.

I’ve been an active user of various Radxa boards through the years (and even post a bit on the forums here, and use a variety of SBCs (these are just a few I’ve tested recently—note 4 Raspberry Pis compared to 20 not-Raspberry Pis

I typically spend more time on Pis mostly because they have great documentation and are kind of the ‘king’ of the SBC world. Hardware-wise they stink in many ways, but hardware is not everything.

Thanks Jeff, you have all my love, with my wife we look at your videos and we like them very much, very informative. Sorry for my previous post. Take care.

Poking around the BIOS .BIN for the X4, I note this:

In-Band ECC Support", Help: "Enable/Disable In-Band ECC. Will be enabled if memory has symmetric configuration . . . OneOfOption Option: “Disabled” Value: 0, Default, MfgDefault

It seems like this is a hidden option (I don’t have an X4 myself to look in the BIOS).

Could this half-channel by why the X4 doesn’t support IBECC compared to other N100/(LP)DDR5 SBCs?