Thanks for your reply.

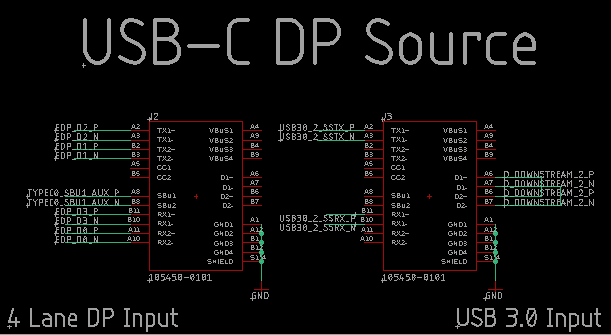

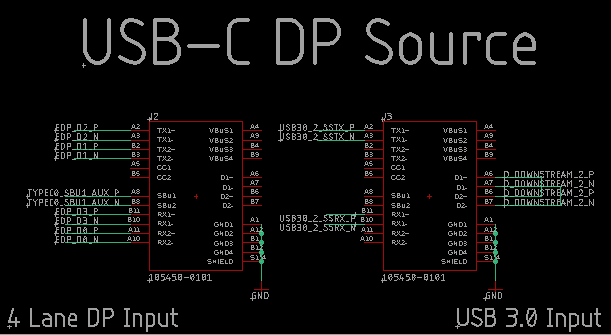

We’ve tried making the following changes below but unfortunately, I wasn’t able to get it to work yet. I need to mux the specific DisplayPort data lanes from the RK3588 GPU as follows, onto the USB-C port pins in a <3 2 0 1> setup, which then will feed into my test PCB. I want to obviously ignore alt mode just for testing purposes and force the DP lanes on the connector.

kernel/drivers/phy/rockchip/phy-rockchip-usbdp.c at d7f6b85f6fcfdf510f382174bf08368e73fb9287 · radxa/kernel · GitHub

These are the changes we made to the device tree. Do they look correct? I need to make sure I’m forcing DP and I need to mux the data lanes as per the rockchip,dp-lane-mux flag below:

12 │ index fcfc141a9ae9..ba04f955ef82 100644

13 │ --- a/arch/arm64/boot/dts/rockchip/rk3588s-radxa-cm5-io.dts

14 │ +++ b/arch/arm64/boot/dts/rockchip/rk3588s-radxa-cm5-io.dts

15 │ @@ -267,77 +267,10 @@ dsi1_backlight: dsi1-backlight {

16 │ &i2c6 {

17 │ status = "okay";

18 │ pinctrl-names = "default";

19 │ pinctrl-0 = <&i2c6m3_xfer>;

20 │

21 │ - usbc0: fusb302@22 {

22 │ - compatible = "fcs,fusb302";

23 │ - reg = <0x22>;

24 │ - interrupt-parent = <&gpio0>;

25 │ - interrupts = <RK_PC4 IRQ_TYPE_LEVEL_LOW>;

26 │ - int-n-gpios = <&gpio0 RK_PC4 GPIO_ACTIVE_LOW>;

27 │ - pinctrl-names = "default";

28 │ - pinctrl-0 = <&usbc0_int>;

29 │ - vbus-supply = <&vbus5v0_typec>;

30 │ - status = "okay";

31 │ -

32 │ - ports {

33 │ - #address-cells = <1>;

34 │ - #size-cells = <0>;

35 │ - port@0 {

36 │ - reg = <0>;

37 │ - usbc0_role_sw: endpoint@0 {

38 │ - remote-endpoint = <&dwc3_0_role_switch>;

39 │ - };

40 │ - };

41 │ - };

42 │ -

43 │ - usb_con: connector {

44 │ - compatible = "usb-c-connector";

45 │ - label = "USB-C";

46 │ - data-role = "dual";

47 │ - power-role = "dual";

48 │ - try-power-role = "sink";

49 │ - op-sink-microwatt = <1000000>;

50 │ -

51 │ - sink-pdos =

52 │ - <PDO_FIXED(5000, 1000, PDO_FIXED_USB_COMM)>;

53 │ - source-pdos =

54 │ - <PDO_FIXED(5000, 3000, PDO_FIXED_USB_COMM)>;

55 │ -

56 │ - altmodes {

57 │ - #address-cells = <1>;

58 │ - #size-cells = <0>;

59 │ -

60 │ - altmode@0 {

61 │ - reg = <0>;

62 │ - svid = <0xff01>;

63 │ - vdo = <0xffffffff>;

64 │ - };

65 │ - };

66 │ -

67 │ - ports {

68 │ - #address-cells = <1>;

69 │ - #size-cells = <0>;

70 │ -

71 │ - port@0 {

72 │ - reg = <0>;

73 │ - usbc0_orien_sw: endpoint {

74 │ - remote-endpoint = <&usbdp_phy0_orientation_switch>;

75 │ - };

76 │ - };

77 │ -

78 │ - port@1 {

79 │ - reg = <1>;

80 │ - dp_altmode_mux: endpoint {

81 │ - remote-endpoint = <&usbdp_phy0_dp_altmode_mux>;

82 │ - };

83 │ - };

84 │ - };

85 │ - };

86 │ - };

87 │ -

88 │ hym8563: hym8563@51 {

89 │ compatible = "haoyu,hym8563";

90 │ reg = <0x51>;

91 │ #clock-cells = <0>;

92 │ clock-frequency = <32768>;

93 │ @@ -349,28 +282,16 @@ hym8563: hym8563@51 {

94 │ };

95 │ };

96 │

97 │ &usbdp_phy0 {

98 │ status = "okay";

99 │ - orientation-switch;

100 │ - svid = <0xff01>;

101 │ - sbu1-dc-gpios = <&gpio3 RK_PC4 GPIO_ACTIVE_HIGH>;

102 │ - sbu2-dc-gpios = <&gpio3 RK_PD4 GPIO_ACTIVE_HIGH>;

103 │ -

104 │ - port {

105 │ - #address-cells = <1>;

106 │ - #size-cells = <0>;

107 │ - usbdp_phy0_orientation_switch: endpoint@0 {

108 │ - reg = <0>;

109 │ - remote-endpoint = <&usbc0_orien_sw>;

110 │ - };

111 │ + rockchip,dp-lane-mux = <3 2 0 1>;

112 │ +};

113 │

114 │ - usbdp_phy0_dp_altmode_mux: endpoint@1 {

115 │ - reg = <1>;

116 │ - remote-endpoint = <&dp_altmode_mux>;

117 │ - };

118 │ - };

119 │ +&route_dp0 {

120 │ + status = "okay";

121 │ + connect = <&vp2_out_dp0>;

122 │ };

123 │

124 │ &dp0 {

125 │ status = "okay";

126 │ };

11 │ diff --git a/arch/arm64/boot/dts/rockchip/rk3588s-radxa-cm5-io.dts b/arch/arm64/boot/dts/rockchip/rk3588s-radxa-cm5-io.dts

12 │ index ba04f955ef82..92b8482f64e1 100644

13 │ --- a/arch/arm64/boot/dts/rockchip/rk3588s-radxa-cm5-io.dts

14 │ +++ b/arch/arm64/boot/dts/rockchip/rk3588s-radxa-cm5-io.dts

15 │ @@ -651,20 +651,10 @@ &usbdrd3_0 {

16 │

17 │ &usbdrd_dwc3_0 {

18 │ dr_mode = "otg";

19 │ extcon = <&u2phy0>;

20 │ status = "okay";

21 │ -

22 │ - usb-role-switch;

23 │ - port {

24 │ - #address-cells = <1>;

25 │ - #size-cells = <0>;

26 │ - dwc3_0_role_switch: endpoint@0 {

27 │ - reg = <0>;

28 │ - remote-endpoint = <&usbc0_role_sw>;

29 │ - };

30 │ - };

31 │ };

32 │

33 │ &usbhost3_0 {

34 │ status = "okay";

35 │ };

For anyone interested in helping debug, I’ve also uploaded my schematics below: