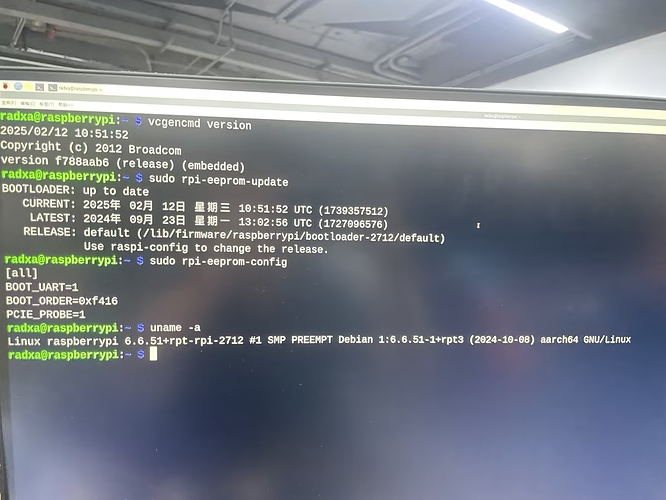

Here is my current EEPROM config (sudo rpi-eeprom-config -e):

[all]

BOOT_UART=1

BOOT_ORDER=0xf146

WAKE_ON_GPIO=0

POWER_OFF_ON_HALT=1

SDRAM_BANKLOW=1

PCIE_PROBE=1

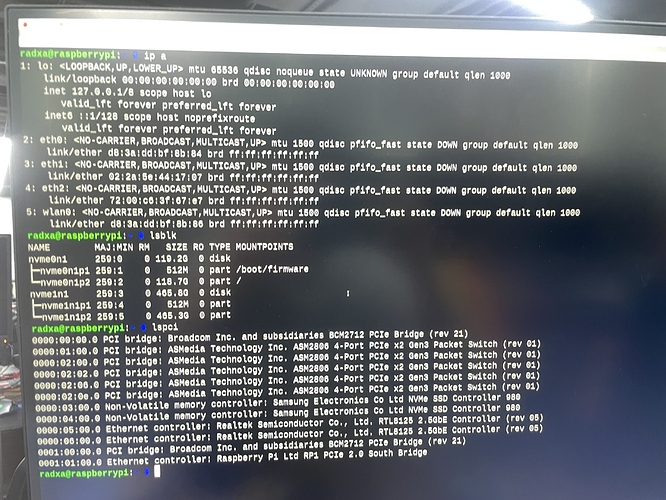

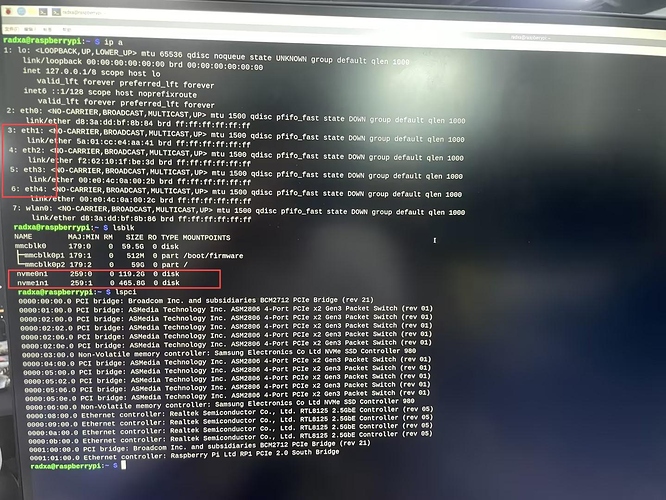

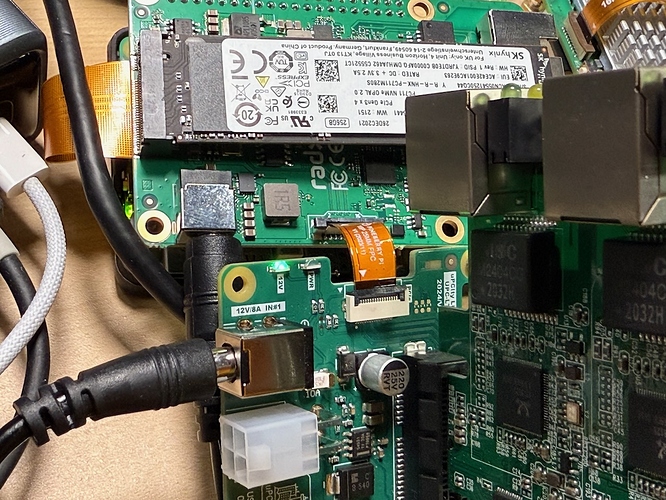

With both boards connected and powered, I am seeing two PCIe switches, but none of the downstream devices except for the NVMe drive (none of the Ethernet ports connected are listed):

pi@pi5-router:~ $ lspci

0000:00:00.0 PCI bridge: Broadcom Inc. and subsidiaries BCM2712 PCIe Bridge (rev 21)

0000:01:00.0 PCI bridge: ASMedia Technology Inc. ASM2806 4-Port PCIe x2 Gen3 Packet Switch (rev 01)

0000:02:00.0 PCI bridge: ASMedia Technology Inc. ASM2806 4-Port PCIe x2 Gen3 Packet Switch (rev 01)

0000:02:02.0 PCI bridge: ASMedia Technology Inc. ASM2806 4-Port PCIe x2 Gen3 Packet Switch (rev 01)

0000:02:06.0 PCI bridge: ASMedia Technology Inc. ASM2806 4-Port PCIe x2 Gen3 Packet Switch (rev 01)

0000:02:0e.0 PCI bridge: ASMedia Technology Inc. ASM2806 4-Port PCIe x2 Gen3 Packet Switch (rev 01)

0000:03:00.0 Non-Volatile memory controller: SK hynix Gold P31/PC711 NVMe Solid State Drive

0000:04:00.0 PCI bridge: ASMedia Technology Inc. ASM2806 4-Port PCIe x2 Gen3 Packet Switch (rev 01)

0000:05:00.0 PCI bridge: ASMedia Technology Inc. ASM2806 4-Port PCIe x2 Gen3 Packet Switch (rev 01)

0000:05:02.0 PCI bridge: ASMedia Technology Inc. ASM2806 4-Port PCIe x2 Gen3 Packet Switch (rev 01)

0000:05:06.0 PCI bridge: ASMedia Technology Inc. ASM2806 4-Port PCIe x2 Gen3 Packet Switch (rev 01)

0000:05:0e.0 PCI bridge: ASMedia Technology Inc. ASM2806 4-Port PCIe x2 Gen3 Packet Switch (rev 01)

0001:00:00.0 PCI bridge: Broadcom Inc. and subsidiaries BCM2712 PCIe Bridge (rev 21)

0001:01:00.0 Ethernet controller: Raspberry Pi Ltd RP1 PCIe 2.0 South Bridge

I did see some PCI bus issues noted in dmesg logs:

Click to expand

pi@pi5-router:~ $ dmesg | grep pci

[ 0.000000] Kernel command line: reboot=w coherent_pool=1M 8250.nr_uarts=1 pci=pcie_bus_safe cgroup_disable=memory numa_policy=interleave numa=fake=8 system_heap.max_order=0 smsc95xx.macaddr=D8:3A:DD:84:FB:3A vc_mem.mem_base=0x3fc00000 vc_mem.mem_size=0x40000000 console=ttyAMA10,115200 console=tty1 root=PARTUUID=78573923-02 rootfstype=ext4 fsck.repair=yes rootwait quiet splash plymouth.ignore-serial-consoles cfg80211.ieee80211_regdom=US

[ 0.024833] /axi/pcie@120000/rp1: Fixed dependency cycle(s) with /axi/pcie@120000/rp1

[ 0.025073] /axi/pcie@120000/rp1: Fixed dependency cycle(s) with /axi/pcie@120000/rp1

[ 0.283569] brcm-pcie 1000110000.pcie: host bridge /axi/pcie@110000 ranges:

[ 0.283575] brcm-pcie 1000110000.pcie: No bus range found for /axi/pcie@110000, using [bus 00-ff]

[ 0.283584] brcm-pcie 1000110000.pcie: MEM 0x1b80000000..0x1bffffffff -> 0x0080000000

[ 0.283588] brcm-pcie 1000110000.pcie: MEM 0x1800000000..0x1b7fffffff -> 0x0400000000

[ 0.283592] brcm-pcie 1000110000.pcie: IB MEM 0x0000000000..0x0fffffffff -> 0x1000000000

[ 0.284932] brcm-pcie 1000110000.pcie: Forcing gen 3

[ 0.285070] brcm-pcie 1000110000.pcie: PCI host bridge to bus 0000:00

[ 0.285072] pci_bus 0000:00: root bus resource [bus 00-ff]

[ 0.285076] pci_bus 0000:00: root bus resource [mem 0x1b80000000-0x1bffffffff] (bus address [0x80000000-0xffffffff])

[ 0.285078] pci_bus 0000:00: root bus resource [mem 0x1800000000-0x1b7fffffff pref] (bus address [0x400000000-0x77fffffff])

[ 0.285088] pci 0000:00:00.0: [14e4:2712] type 01 class 0x060400

[ 0.285108] pci 0000:00:00.0: PME# supported from D0 D3hot

[ 0.393364] brcm-pcie 1000110000.pcie: link up, 8.0 GT/s PCIe x1 (!SSC)

[ 0.393407] pci 0000:01:00.0: [1b21:2806] type 01 class 0x060400

[ 0.393443] pci 0000:01:00.0: enabling Extended Tags

[ 0.393510] pci 0000:01:00.0: PME# supported from D0 D3hot D3cold

[ 0.393548] pci 0000:01:00.0: 7.876 Gb/s available PCIe bandwidth, limited by 8.0 GT/s PCIe x1 link at 0000:00:00.0 (capable of 15.752 Gb/s with 8.0 GT/s PCIe x2 link)

[ 0.405368] pci 0000:01:00.0: bridge configuration invalid ([bus 00-00]), reconfiguring

[ 0.405438] pci 0000:02:00.0: [1b21:2806] type 01 class 0x060400

[ 0.405474] pci 0000:02:00.0: enabling Extended Tags

[ 0.405537] pci 0000:02:00.0: PME# supported from D0 D3hot D3cold

[ 0.405807] pci 0000:02:02.0: [1b21:2806] type 01 class 0x060400

[ 0.405843] pci 0000:02:02.0: enabling Extended Tags

[ 0.405906] pci 0000:02:02.0: PME# supported from D0 D3hot D3cold

[ 0.406065] pci 0000:02:06.0: [1b21:2806] type 01 class 0x060400

[ 0.406100] pci 0000:02:06.0: enabling Extended Tags

[ 0.406163] pci 0000:02:06.0: PME# supported from D0 D3hot D3cold

[ 0.406377] pci 0000:02:0e.0: [1b21:2806] type 01 class 0x060400

[ 0.406412] pci 0000:02:0e.0: enabling Extended Tags

[ 0.406475] pci 0000:02:0e.0: PME# supported from D0 D3hot D3cold

[ 0.406835] pci 0000:02:00.0: bridge configuration invalid ([bus 00-00]), reconfiguring

[ 0.406841] pci 0000:02:02.0: bridge configuration invalid ([bus 00-00]), reconfiguring

[ 0.406847] pci 0000:02:06.0: bridge configuration invalid ([bus 00-00]), reconfiguring

[ 0.406853] pci 0000:02:0e.0: bridge configuration invalid ([bus 00-00]), reconfiguring

[ 0.406915] pci 0000:03:00.0: [1c5c:174a] type 00 class 0x010802

[ 0.406938] pci 0000:03:00.0: reg 0x10: [mem 0x00000000-0x00003fff 64bit]

[ 0.406946] pci 0000:03:00.0: reg 0x18: [mem 0x00000000-0x00000fff]

[ 0.406954] pci 0000:03:00.0: reg 0x1c: [mem 0x00000000-0x00000fff]

[ 0.407143] pci 0000:03:00.0: 7.876 Gb/s available PCIe bandwidth, limited by 8.0 GT/s PCIe x1 link at 0000:00:00.0 (capable of 31.504 Gb/s with 8.0 GT/s PCIe x4 link)

[ 0.417378] pci_bus 0000:03: busn_res: [bus 03-06] end is updated to 03

[ 0.417438] pci 0000:04:00.0: [1b21:2806] type 01 class 0x060400

[ 0.417491] pci 0000:04:00.0: enabling Extended Tags

[ 0.417584] pci 0000:04:00.0: PME# supported from D0 D3hot D3cold

[ 0.417641] pci 0000:04:00.0: 7.876 Gb/s available PCIe bandwidth, limited by 8.0 GT/s PCIe x1 link at 0000:00:00.0 (capable of 63.008 Gb/s with 8.0 GT/s PCIe x8 link)

[ 0.429368] pci 0000:04:00.0: bridge configuration invalid ([bus 00-00]), reconfiguring

[ 0.429443] pci 0000:05:00.0: [1b21:2806] type 01 class 0x060400

[ 0.429498] pci 0000:05:00.0: enabling Extended Tags

[ 0.429599] pci 0000:05:00.0: PME# supported from D0 D3hot D3cold

[ 0.429766] pci 0000:05:02.0: [1b21:2806] type 01 class 0x060400

[ 0.429821] pci 0000:05:02.0: enabling Extended Tags

[ 0.429922] pci 0000:05:02.0: PME# supported from D0 D3hot D3cold

[ 0.430111] pci 0000:05:06.0: [1b21:2806] type 01 class 0x060400

[ 0.430165] pci 0000:05:06.0: enabling Extended Tags

[ 0.430266] pci 0000:05:06.0: PME# supported from D0 D3hot D3cold

[ 0.430518] pci 0000:05:0e.0: [1b21:2806] type 01 class 0x060400

[ 0.430573] pci 0000:05:0e.0: enabling Extended Tags

[ 0.430673] pci 0000:05:0e.0: PME# supported from D0 D3hot D3cold

[ 0.431070] pci 0000:05:00.0: bridge configuration invalid ([bus 00-00]), reconfiguring

[ 0.431078] pci 0000:05:02.0: bridge configuration invalid ([bus 00-00]), reconfiguring

[ 0.431086] pci 0000:05:06.0: bridge configuration invalid ([bus 00-00]), reconfiguring

[ 0.431095] pci 0000:05:0e.0: bridge configuration invalid ([bus 00-00]), reconfiguring

[ 0.431169] pci_bus 0000:06: busn_res: [bus 06] end is updated to 06

[ 0.431220] pci_bus 0000:07: busn_res: can not insert [bus 07-06] under [bus 05-06] (conflicts with (null) [bus 05-06])

[ 0.431241] pci_bus 0000:07: busn_res: [bus 07-06] end is updated to 07

[ 0.431243] pci_bus 0000:07: busn_res: can not insert [bus 07] under [bus 05-06] (conflicts with (null) [bus 05-06])

[ 0.431245] pci 0000:05:02.0: devices behind bridge are unusable because [bus 07] cannot be assigned for them

[ 0.431295] pci_bus 0000:08: busn_res: can not insert [bus 08-06] under [bus 05-06] (conflicts with (null) [bus 05-06])

[ 0.431315] pci_bus 0000:08: busn_res: [bus 08-06] end is updated to 08

[ 0.431317] pci_bus 0000:08: busn_res: can not insert [bus 08] under [bus 05-06] (conflicts with (null) [bus 05-06])

[ 0.431319] pci 0000:05:06.0: devices behind bridge are unusable because [bus 08] cannot be assigned for them

[ 0.431369] pci_bus 0000:09: busn_res: can not insert [bus 09-06] under [bus 05-06] (conflicts with (null) [bus 05-06])

[ 0.431389] pci_bus 0000:09: busn_res: [bus 09-06] end is updated to 09

[ 0.431391] pci_bus 0000:09: busn_res: can not insert [bus 09] under [bus 05-06] (conflicts with (null) [bus 05-06])

[ 0.431393] pci 0000:05:0e.0: devices behind bridge are unusable because [bus 09] cannot be assigned for them

[ 0.431396] pci_bus 0000:05: busn_res: [bus 05-06] end can not be updated to 09

[ 0.431401] pci_bus 0000:04: busn_res: [bus 04-06] end can not be updated to 09

[ 0.431437] pci_bus 0000:0a: busn_res: can not insert [bus 0a-06] under [bus 02-06] (conflicts with (null) [bus 02-06])

[ 0.431456] pci_bus 0000:0a: busn_res: [bus 0a-06] end is updated to 0a

[ 0.431458] pci_bus 0000:0a: busn_res: can not insert [bus 0a] under [bus 02-06] (conflicts with (null) [bus 02-06])

[ 0.431460] pci 0000:02:06.0: devices behind bridge are unusable because [bus 0a] cannot be assigned for them

[ 0.431495] pci_bus 0000:0b: busn_res: can not insert [bus 0b-06] under [bus 02-06] (conflicts with (null) [bus 02-06])

[ 0.431514] pci_bus 0000:0b: busn_res: [bus 0b-06] end is updated to 0b

[ 0.431516] pci_bus 0000:0b: busn_res: can not insert [bus 0b] under [bus 02-06] (conflicts with (null) [bus 02-06])

[ 0.431518] pci 0000:02:0e.0: devices behind bridge are unusable because [bus 0b] cannot be assigned for them

[ 0.431520] pci_bus 0000:02: busn_res: [bus 02-06] end can not be updated to 0b

[ 0.431524] pci 0000:00:00.0: bridge has subordinate 06 but max busn 0b

[ 0.431535] pci 0000:00:00.0: BAR 8: assigned [mem 0x1b80000000-0x1b800fffff]

[ 0.431537] pci 0000:01:00.0: BAR 8: assigned [mem 0x1b80000000-0x1b800fffff]

[ 0.431540] pci 0000:02:00.0: BAR 8: assigned [mem 0x1b80000000-0x1b800fffff]

[ 0.431542] pci 0000:03:00.0: BAR 0: assigned [mem 0x1b80000000-0x1b80003fff 64bit]

[ 0.431554] pci 0000:03:00.0: BAR 2: assigned [mem 0x1b80004000-0x1b80004fff]

[ 0.431558] pci 0000:03:00.0: BAR 3: assigned [mem 0x1b80005000-0x1b80005fff]

[ 0.431563] pci 0000:02:00.0: PCI bridge to [bus 03]

[ 0.431567] pci 0000:02:00.0: bridge window [mem 0x1b80000000-0x1b800fffff]

[ 0.431573] pci 0000:05:00.0: PCI bridge to [bus 06]

[ 0.431585] pci 0000:05:02.0: PCI bridge to [bus 07]

[ 0.431598] pci 0000:05:06.0: PCI bridge to [bus 08]

[ 0.431611] pci 0000:05:0e.0: PCI bridge to [bus 09]

[ 0.431624] pci 0000:04:00.0: PCI bridge to [bus 05-06]

[ 0.431637] pci 0000:02:02.0: PCI bridge to [bus 04-06]

[ 0.431645] pci 0000:02:06.0: PCI bridge to [bus 0a]

[ 0.431654] pci 0000:02:0e.0: PCI bridge to [bus 0b]

[ 0.431663] pci 0000:01:00.0: PCI bridge to [bus 02-06]

[ 0.431666] pci 0000:01:00.0: bridge window [mem 0x1b80000000-0x1b800fffff]

[ 0.431672] pci 0000:00:00.0: PCI bridge to [bus 01-06]

[ 0.431674] pci 0000:00:00.0: bridge window [mem 0x1b80000000-0x1b800fffff]

[ 0.431678] pci 0000:00:00.0: Max Payload Size set to 512/ 512 (was 128), Max Read Rq 512

[ 0.431684] pci 0000:01:00.0: Max Payload Size set to 512/ 512 (was 128), Max Read Rq 512

[ 0.431690] pci 0000:02:00.0: Max Payload Size set to 512/ 512 (was 128), Max Read Rq 512

[ 0.431699] pci 0000:03:00.0: Max Payload Size set to 512/ 512 (was 128), Max Read Rq 512

[ 0.431705] pci 0000:02:02.0: Max Payload Size set to 512/ 512 (was 128), Max Read Rq 512

[ 0.431713] pci 0000:04:00.0: Max Payload Size set to 512/ 512 (was 128), Max Read Rq 512

[ 0.431722] pci 0000:05:00.0: Max Payload Size set to 512/ 512 (was 128), Max Read Rq 512

[ 0.431730] pci 0000:05:02.0: Max Payload Size set to 512/ 512 (was 128), Max Read Rq 512

[ 0.431738] pci 0000:05:06.0: Max Payload Size set to 512/ 512 (was 128), Max Read Rq 512

[ 0.431747] pci 0000:05:0e.0: Max Payload Size set to 512/ 512 (was 128), Max Read Rq 512

[ 0.431752] pci 0000:02:06.0: Max Payload Size set to 512/ 512 (was 128), Max Read Rq 512

[ 0.431758] pci 0000:02:0e.0: Max Payload Size set to 512/ 512 (was 128), Max Read Rq 512

[ 0.431846] pcieport 0000:00:00.0: enabling device (0000 -> 0002)

[ 0.431879] pcieport 0000:00:00.0: PME: Signaling with IRQ 38

[ 0.432034] pcieport 0000:00:00.0: AER: enabled with IRQ 38

[ 0.432087] pcieport 0000:01:00.0: enabling device (0000 -> 0002)

[ 0.432159] pcieport 0000:02:00.0: enabling device (0000 -> 0002)

[ 0.432690] nvme nvme0: pci function 0000:03:00.0

[ 0.469551] brcm-pcie 1000110000.pcie: clkreq control enabled

[ 0.469604] brcm-pcie 1000120000.pcie: host bridge /axi/pcie@120000 ranges:

[ 0.469607] brcm-pcie 1000120000.pcie: No bus range found for /axi/pcie@120000, using [bus 00-ff]

[ 0.469613] brcm-pcie 1000120000.pcie: MEM 0x1f00000000..0x1ffffffffb -> 0x0000000000

[ 0.469617] brcm-pcie 1000120000.pcie: MEM 0x1c00000000..0x1effffffff -> 0x0400000000

[ 0.469621] brcm-pcie 1000120000.pcie: IB MEM 0x1f00000000..0x1f003fffff -> 0x0000000000

[ 0.469625] brcm-pcie 1000120000.pcie: IB MEM 0x0000000000..0x0fffffffff -> 0x1000000000

[ 0.470686] brcm-pcie 1000120000.pcie: Forcing gen 2

[ 0.470710] brcm-pcie 1000120000.pcie: PCI host bridge to bus 0001:00

[ 0.470712] pci_bus 0001:00: root bus resource [bus 00-ff]

[ 0.470714] pci_bus 0001:00: root bus resource [mem 0x1f00000000-0x1ffffffffb] (bus address [0x00000000-0xfffffffb])

[ 0.470717] pci_bus 0001:00: root bus resource [mem 0x1c00000000-0x1effffffff pref] (bus address [0x400000000-0x6ffffffff])

[ 0.470723] pci 0001:00:00.0: [14e4:2712] type 01 class 0x060400

[ 0.470739] pci 0001:00:00.0: PME# supported from D0 D3hot

[ 0.471313] pci 0001:00:00.0: bridge configuration invalid ([bus 00-00]), reconfiguring

[ 0.577357] brcm-pcie 1000120000.pcie: link up, 5.0 GT/s PCIe x4 (!SSC)

[ 0.577374] pci 0001:01:00.0: [1de4:0001] type 00 class 0x020000

[ 0.577386] pci 0001:01:00.0: reg 0x10: [mem 0xffffc000-0xffffffff]

[ 0.577392] pci 0001:01:00.0: reg 0x14: [mem 0xffc00000-0xffffffff]

[ 0.577398] pci 0001:01:00.0: reg 0x18: [mem 0xffff0000-0xffffffff]

[ 0.577459] pci 0001:01:00.0: supports D1

[ 0.577461] pci 0001:01:00.0: PME# supported from D0 D1 D3hot D3cold

[ 0.589363] pci_bus 0001:01: busn_res: [bus 01-ff] end is updated to 01

[ 0.589370] pci 0001:00:00.0: BAR 8: assigned [mem 0x1f00000000-0x1f005fffff]

[ 0.589373] pci 0001:01:00.0: BAR 1: assigned [mem 0x1f00000000-0x1f003fffff]

[ 0.589377] pci 0001:01:00.0: BAR 2: assigned [mem 0x1f00400000-0x1f0040ffff]

[ 0.589381] pci 0001:01:00.0: BAR 0: assigned [mem 0x1f00410000-0x1f00413fff]

[ 0.589385] pci 0001:00:00.0: PCI bridge to [bus 01]

[ 0.589387] pci 0001:00:00.0: bridge window [mem 0x1f00000000-0x1f005fffff]

[ 0.589390] pci 0001:00:00.0: Max Payload Size set to 256/ 512 (was 128), Max Read Rq 512

[ 0.589397] pci 0001:01:00.0: Max Payload Size set to 256/ 256 (was 128), Max Read Rq 512

[ 0.589428] pcieport 0001:00:00.0: enabling device (0000 -> 0002)

[ 0.589447] pcieport 0001:00:00.0: PME: Signaling with IRQ 48

[ 0.589509] pcieport 0001:00:00.0: AER: enabled with IRQ 48

I’ve tried with both dtparam=pciex1_gen=2 and dtparam=pciex1_gen=1 in my /boot/firmware/config.txt, same result.

And just unplugging the 2nd Dual 2.5G HAT allows the first two ports to enumerate again:

pi@pi5-router:~ $ lspci

0000:00:00.0 PCI bridge: Broadcom Inc. and subsidiaries BCM2712 PCIe Bridge (rev 21)

0000:01:00.0 PCI bridge: ASMedia Technology Inc. ASM2806 4-Port PCIe x2 Gen3 Packet Switch (rev 01)

0000:02:00.0 PCI bridge: ASMedia Technology Inc. ASM2806 4-Port PCIe x2 Gen3 Packet Switch (rev 01)

0000:02:02.0 PCI bridge: ASMedia Technology Inc. ASM2806 4-Port PCIe x2 Gen3 Packet Switch (rev 01)

0000:02:06.0 PCI bridge: ASMedia Technology Inc. ASM2806 4-Port PCIe x2 Gen3 Packet Switch (rev 01)

0000:02:0e.0 PCI bridge: ASMedia Technology Inc. ASM2806 4-Port PCIe x2 Gen3 Packet Switch (rev 01)

0000:03:00.0 Non-Volatile memory controller: SK hynix Gold P31/PC711 NVMe Solid State Drive

0000:05:00.0 Ethernet controller: Realtek Semiconductor Co., Ltd. RTL8125 2.5GbE Controller (rev 05)

0000:06:00.0 Ethernet controller: Realtek Semiconductor Co., Ltd. RTL8125 2.5GbE Controller (rev 05)

0001:00:00.0 PCI bridge: Broadcom Inc. and subsidiaries BCM2712 PCIe Bridge (rev 21)

0001:01:00.0 Ethernet controller: Raspberry Pi Ltd RP1 PCIe 2.0 South Bridge