Hi, I am trying to interface and add support of waveshare 7 inch c panel for my radxa cm3 AOSP Build-

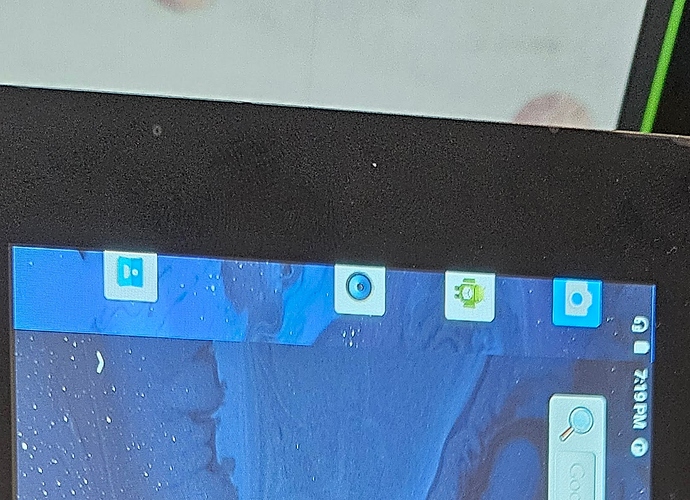

Although I am able to get the display to enable, backlit and show picture, there’s a strange offset, that just can’t seem to go.

The display is wrapping around weirdly.

When referencing the port of raspberry pi 7 inch display I found the timings are different than upstream drivers and going more level I realized that de-mipi-dsi.c seems to handle the display timings different than raspberry pi.

for reference of raspberry pi display -

Radxa Version :

static const struct drm_display_mode raspits_tc358762_mode = {

.clock = 26101800 / 1000,

.hdisplay = 800,

.hsync_start = 800 + 1,

.hsync_end = 800 + 1 + 2,

.htotal = 800 + 1 + 2 + 52,

.vdisplay = 480,

.vsync_start = 480 + 7,

.vsync_end = 480 + 7 + 2,

.vtotal = 480 + 7 + 2 + 21,

.vrefresh = 60,

.flags = DRM_MODE_FLAG_NVSYNC | DRM_MODE_FLAG_NHSYNC,

};

Raspberry Pi Version :

static const struct drm_display_mode raspberrypi_7inch_mode = {

.clock = 30000,

.hdisplay = 800,

.hsync_start = 800 + 131,

.hsync_end = 800 + 131 + 2,

.htotal = 800 + 131 + 2 + 45,

.vdisplay = 480,

.vsync_start = 480 + 7,

.vsync_end = 480 + 7 + 2,

.vtotal = 480 + 7 + 2 + 22,

.flags = DRM_MODE_FLAG_NVSYNC | DRM_MODE_FLAG_NHSYNC,

};

Now My problem is, that I have tried so many iterations like literally for a week, and I am stuck as I think it’s an issue with the calculation of timings itself.

My Display has the following timings -

Waveshare 7 Inch C Panel

–

static const struct drm_display_mode ws_panel_7_0_c_mode = {

.clock = 50000,

.hdisplay = 1024,

.hsync_start = 1024 + 100,

.hsync_end = 1024 + 100 + 100,

.htotal = 1024 + 100 + 100 + 100,

.vdisplay = 600,

.vsync_start = 600 + 10,

.vsync_end = 600 + 10 + 10,

.vtotal = 600 + 10 + 10 + 10,

};

static const struct ws_panel_data ws_panel_7_0_c_data = {

.mode = &ws_panel_7_0_c_mode,

.lanes = 2,

.mode_flags = MIPI_DSI_MODE_VIDEO_HSE | MIPI_DSI_MODE_VIDEO | MIPI_DSI_CLOCK_NON_CONTINUOUS,

};

Can Anyone from Radxa team can look into this and tell why are timings different than raspberry pi and what’d be the compatible timings for this waveshare panel that’ll make the wrap go away.

Thanks