Thank you for your reply.

Booting the board into maskrom mode does not change the connection issue.

I am still receiving: Error connecting DP: cannot read IDR.

This would make me conclude that there must be a physical connection issue, if you manage to receive a connection from maskrom mode.

- (Detour) What version of openocd do you use? In the latest version there is no -ctibase option in target create.

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

Info : FTDI SWD mode enabled

DEPRECATED! use 'adapter speed' not 'adapter_khz'

Warn : Transport "swd" was already selected

./rk3328.cfg:16: Error: Unknown param: -ctibase, try one of: -type, -event, -work-area-virt, -work-area-phys, -work-area-size, -work-area-backup, -endian, -coreid, -chain-position, -dbgbase, -rtos, -defer-examine, -gdb-port, or -gdb-max-connections

in procedure 'script'

at file "embedded:startup.tcl", line 28

at file "./rk3328.cfg", line 16

maskrom mode:

sudo rkdeveloptool ld

DevNo=1 Vid=0x2207,Pid=0x350b,LocationID=104 Maskrom

openocd connection issue:

sudo openocd -f ./olimex-arm-usb-tiny-h2.cfg -f ./rk3328.cfg

Open On-Chip Debugger 0.12.0-01004-g9ea7f3d64 (2024-12-27-21:22)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

Info : FTDI SWD mode enabled

DEPRECATED! use 'adapter speed' not 'adapter_khz'

Warn : Transport "swd" was already selected

Info : Listening on port 6666 for tcl connections

Info : Listening on port 4444 for telnet connections

Info : clock speed 4000 kHz

Error: Error connecting DP: cannot read IDR

target.cfg:

#

# Rock-Chip RK3328

#

adapter_khz 4000

transport select swd

set _CHIPNAME rk3328

set _TARGETNAME $_CHIPNAME.cpu

set _ENDIAN little

swd newdap $_CHIPNAME cpu none

dap create $_CHIPNAME.dap -chain-position $_CHIPNAME.cpu

target create ${_TARGETNAME}0 cortex_a -dap $_CHIPNAME.dap \

-coreid 0 -dbgbase 0x81040000

# -ctibase 0x81014000

#

target smp ${_TARGETNAME}0

${_TARGETNAME}0 configure -event reset-assert-post "cortex_a dbginit"

debugger.cfg:

# SPDX-License-Identifier: GPL-2.0-or-later

#

# Olimex ARM-USB-TINY-H

#

# http://www.olimex.com/dev/arm-usb-tiny-h.html

#

adapter driver ftdi

transport select swd

ftdi device_desc "Olimex OpenOCD JTAG ARM-USB-TINY-H"

ftdi vid_pid 0x15ba 0x002a

ftdi layout_init 0x0808 0x0a1b

ftdi layout_signal nSRST -oe 0x0200

ftdi layout_signal nTRST -data 0x0100 -oe 0x0100

ftdi layout_signal LED -data 0x0800

# Map FTDI GPIO pins for SWD

ftdi layout_signal SWCLK -data 0x0100 -oe 0x0100

ftdi layout_signal SWDIO -data 0x0200 -oe 0x0200

ftdi layout_signal SWD_EN -data 0x0000 -oe 0x0000

lsusb:

Bus 001 Device 005: ID 15ba:002a Olimex Ltd. ARM-USB-TINY-H JTAG interface

dmsg:

[190208.771978] usb 1-6: new high-speed USB device number 5 using xhci_hcd

[190208.903042] usb 1-6: New USB device found, idVendor=15ba, idProduct=002a, bcdDevice= 7.00

[190208.903054] usb 1-6: New USB device strings: Mfr=1, Product=2, SerialNumber=3

[190208.903064] usb 1-6: Product: Olimex OpenOCD JTAG ARM-USB-TINY-H

[190208.903068] usb 1-6: SerialNumber: OL44653F

[190208.912563] ftdi_sio 1-6:1.1: FTDI USB Serial Device converter detected

[190208.912644] usb 1-6: Detected FT2232H

[190208.912846] usb 1-6: FTDI USB Serial Device converter now attached to ttyUSB0

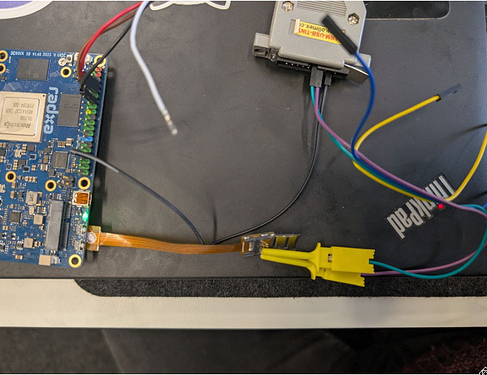

- For the wiring. I currently do not have a multi meter. But it is only 3 pins I am connecting.

Let me walk you through my steps, maybe you have some idea what I forgot.

-

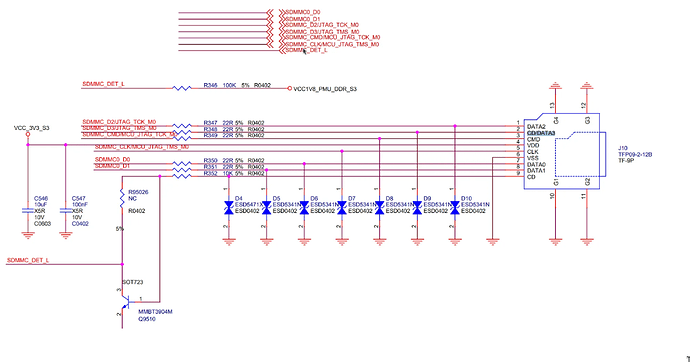

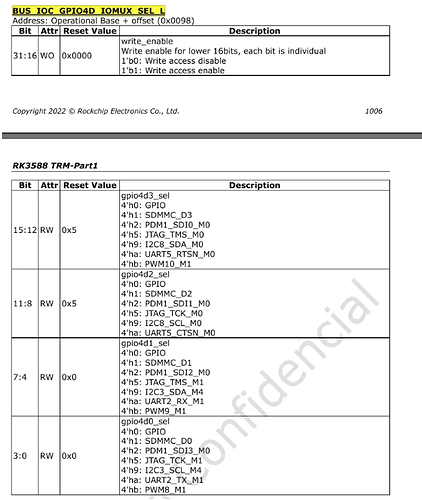

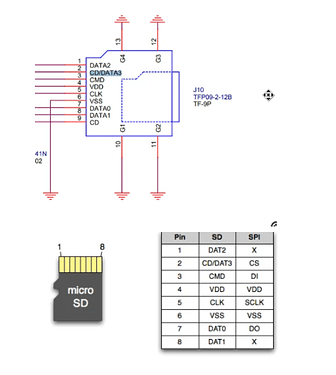

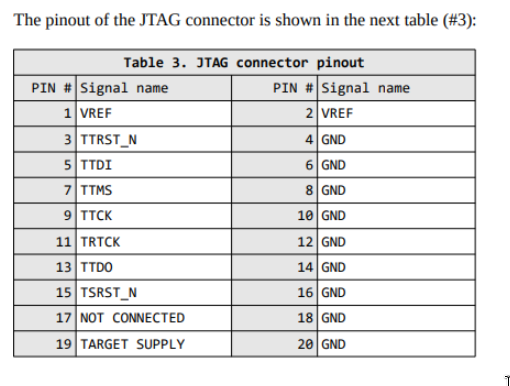

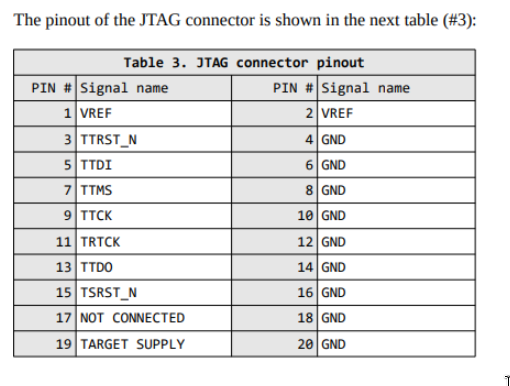

Sdcard Pin1: Data2 -> SDMMC_D2/JTAG_TCK_M0 -> TTCK on jtag connector -> Pin 9

-

Sdcard Pin2: CD/Data3 -> SDMMC_D3/JTAG_TMS_M0 -> TTMS on jtag connector -> Pin 7

-

Connect GPIO ground pin on board with any ground pin on the JTAG connector

Do you have some ideas? Or perhaps a working configuration for your setup you can point me to?

Any help is greatly appreciated.