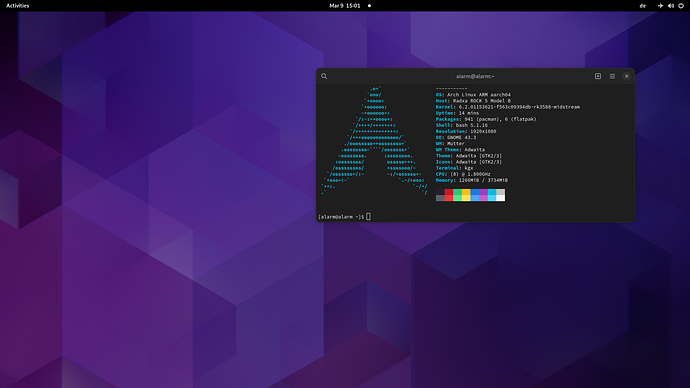

I don’t know exactly but did some further testings right now (quite time consuming), I’m testing with an Armbian image that combines @Googulator’s kernel with Radxa’s/Rockchip’s u-boot/BLOBs. As such situation with mainline u-boot might be completely different but I don’t even know whether this works or not.

At least in this special scenario (RK’s BSP u-boot and firmware BLOBs combined with the 6.2 midstream kernel) it looks like this when clocking the DRAM at 2112 MHz and keeping the CPU cores at ~400 MHz:

Idle consumption vs. cpu4 being fully loaded with cpuminer (taskset -c 4 /usr/local/src/cpuminer-multi/cpuminer --benchmark --cpu-priority=2):

- 5.10.110: 1920 mW vs. 2440 mW = 520 mW difference

- 6.2-midstream: 3410 mW vs. 3950 mW = 540 mW difference

So at least the difference is the same and we already know that clocking the DRAM between 528 MHz and 2112 MHz makes up for a 500-600 mW difference. The 6.2 midterm kernel currently lacks a DMC driver or it is not active as such these 500-600 mW higher idle consumption are to be expected.

For the remaining ~1500mW difference I would suspect RK’s u-boot bringing up the hardware in a state that is expected to be controlled afterwards by RK’s BSP kernel but this stuff is missing with the midstream kernel (yet).

Applies to every RK35xx SoC right now as long as it’s running RK’s BSP bootloader (u-boot + BLOBs) since then PVTM does its own thing. By tweaking the DVFS OPP tables one can convince PVTM to clock higher. That’s why on my RK3588 with @Googulator’s kernel and the overvolted A55 OPP the little cores clock north of 1900 MHz. And the same can be done with the A76. @amazingfate for example managed to get them clocked beyond 2700 MHz just by tweaking the supply voltages. The cpufreq driver still reports 2400 MHz while in reality it’s way above or below.

But all of this only works as long as RK’s BSP u-boot + boot BLOBs are in place and with a true mainline bootloader situation something different might happen (that’s why I think Collabora’s Sebastian has eliminated the DVFS OPP beyond 2.2 GHz).