@kwisatz Hi , firstly I think you have done some excellent research in this thread , and it has inspired and equipped to implement the overlay for the Waveshare CAN hat onto the Radxa Zero . I had done something similiar for RockPi S , but AMlogic resources and examples are in short supply on the internet.

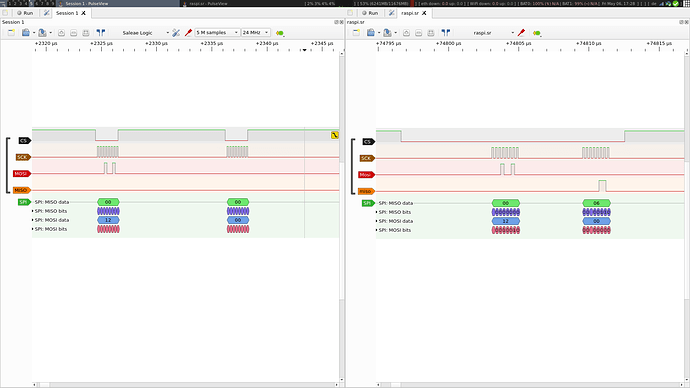

The CAN hat employs Microchip MCP2515 , but its interface is not unlike the enc 28j60, meaning it has a SPI interface and a GPIO external IRQ interface. So with your help I have compiled the following dts source, and it works perfectly . Don’t know why I don’t have any SPI issues , could be because the packets are smaller and less frequent than Ethernet.

Blockquote /dts-v1/;

/plugin/;

/ {

compatible = “radxa,zero”, “amlogic,g12a”;

fragment@0

{

target-path = "/";

__overlay__

{

can_mcp2515_osc: can_mcp2515_oscs

{

compatible = "fixed-clock";

clock-frequency = <12000000>;

#clock-cells = <0>;

};

};

};

fragment@1

{

target = <&gpio>;

__overlay__

{

mcp2515_int_pin: mcp2515_int_pin@0

{

amlogic,pins = <&gpio 48>; /* or is it <&gpio 85> ? */

amlogic,function = "irq"; /* in - whether "out" (1) or "in" (0) */

// amlogic,function = <0>; /* in - whether "out" (1) or "in" (0) */

amlogic,pull = <0>;

};

};

};

fragment@3

{

target = <&spicc1>;

__overlay__

{

pinctrl-0 = <&spicc1_pins &spicc1_ss0_pins>;

pinctrl-names = "default";

#address-cells = <1>;

#size-cells = <0>;

status = "okay";

mcp2515: spidev@0

{

compatible = "microchip,mcp2515";

reg = <0>;

interrupt-parent = <&gpio_intc>;

interrupts = <60 2>;

spi-max-frequency = <12000000>;

clocks = <&can_mcp2515_osc>;

pinctrl-0 = <&mcp2515_int_pin>;

};

};

};

};

As you can see I am using SPI1 (SPIB per gpio pinout diagram) and i am using GPIOC_7 as the GPIO IRQ input. Gpio number 48 represents the GPIOC_7 and the IRQ number 60 the IRQ mapping for GPIOC_7. The latter I got from your link table below :

- 223:100 undefined (no interrupt)

- 99:97 3 pins on bank GPIOE

- 96:77 20 pins on bank GPIOX

- 76:61 16 pins on bank GPIOA

- 60:53 8 pins on bank GPIOC

- 52:37 16 pins on bank BOOT

- 36:28 9 pins on bank GPIOH

- 27:12 16 pins on bank GPIOZ

- 11:0 12 pins in the AO domain

So thank my man , you did some great work here . Have you managed success regarding your ethernet interface ?

Kind Regards

Anton

So, changing to GPIOC_7, number 60.

So, changing to GPIOC_7, number 60.