Thanks for the feedback @RadxaYuntian

- How does one know to use

&gicasinterrupt-parentand not&gpio_intc? Both are tagged asinterrupt controllerand it was my understanding that I’d pick the one that is closest (in the tree) to the device node I’m describing. - You mention interrupts 81 and 82.

spicc1actually uses90and since the value90is not anywhere withinmeson-g12a-gpio.hI am confused as to how interrupt lines map to GPIO pins? So even if I could put 91 in this case, I still don’t know which pin to connect the interrupt line to. - What do these numbers stand for and how does one learn which is which?

- What would you be able to do/check if you had the hardware module?

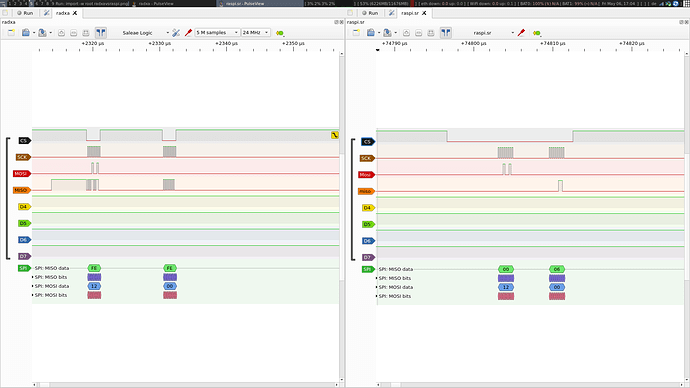

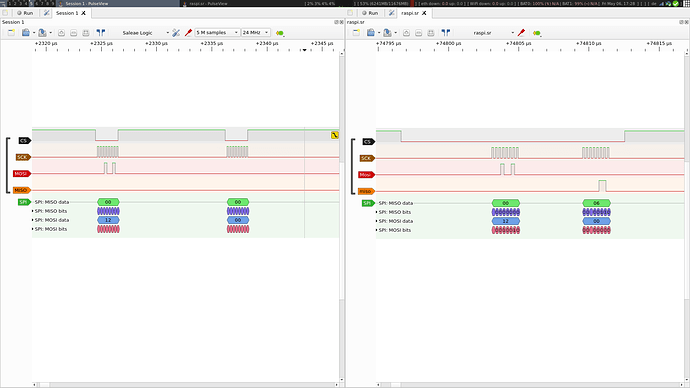

Without defining the interrupt-parent or interrupts, the results stay the same:

[ 3.843415] enc28j60 spi1.0: Ethernet driver 1.02 loaded

[ 3.849474] enc28j60 spi1.0: chip not found

[ 3.849597] enc28j60: probe of spi1.0 failed with error -5

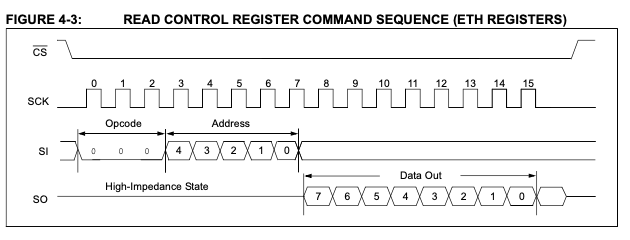

Maybe what isn’t entirely clear here is that the enc28j60 module has an interrupt pin and from what I read elsewhere, the module won’t work without this pin being connected.

So, the interrupt-line must IMHO map to a GPIO pin. I do not currently see how this is done.

My hypothesis is thus that the correct interrupt-parent is actually the gpio_intc and not gic directly.

gpio_intc: interrupt-controller@f080 {

compatible = "amlogic,meson-g12a-gpio-intc",

"amlogic,meson-gpio-intc";

reg = <0x0 0xf080 0x0 0x10>;

interrupt-controller;

#interrupt-cells = <2>;

amlogic,channel-interrupts = <64 65 66 67 68 69 70 71>;

};

If this hypothesis is correct, I still need to figure out how to map physical GPIO pins to register indices within gpio_intc.

For reference, the raspberry-pi dts has this:

fragment@2 {

target = <&spi0>;

__overlay__ {

/* needed to avoid dtc warning */

#address-cells = <1>;

#size-cells = <0>;

status = "okay";

eth1: enc28j60@0{

compatible = "microchip,enc28j60";

reg = <0>; /* CE0 */

pinctrl-names = "default";

pinctrl-0 = <ð1_pins>;

interrupt-parent = <&gpio>;

interrupts = <25 0x2>; /* falling edge */

spi-max-frequency = <12000000>;

status = "okay";

};

};

};

fragment@3 {

target = <&gpio>;

__overlay__ {

eth1_pins: eth1_pins {

brcm,pins = <25>;

brcm,function = <0>; /* in */

brcm,pull = <0>; /* none */

};

};

};

I also don’t know exactly how, but the value 25 here refers to their GPIO25 which is pin 22.

The same value is used below in the definition of the pins as well as above when specifying interrupts.

So, changing to GPIOC_7, number 60.

So, changing to GPIOC_7, number 60.